请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC38RF80EVM 主题中讨论的其他器件:LMK04828

你(们)好

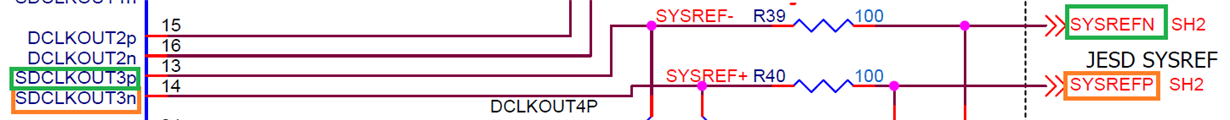

在 LMK04828和 DAC38RF8xEVM 的参考设计表5中、SYSREF (P、N)输出连接到器件上的错误引脚。 SYSREFN 连接到 SDCLKOUT3p、SYSREFP 连接到 SDCLKOUT3n。

我想使用 FPGA 板评估设计。 我使用的是 Rev E 原理图、我认为它是最新的。 由于我在社区中找不到任何关于这方面的问题、我假设评估 板按预期工作。

有人能解释一下、即使以错误的方式进行连接、它也是如何工作的? TI 是否知道这一点并计划纠正这个 scehmatic?

此致

锡