Other Parts Discussed in Thread: ADS58J64, LMK04828, ADS54J64EVM, ADS54J64, ADS58J64EVM

主题中讨论的其他器件:ADS58J64、 LMK04828、 ADS54J64、 ADS58J64EVM

你好

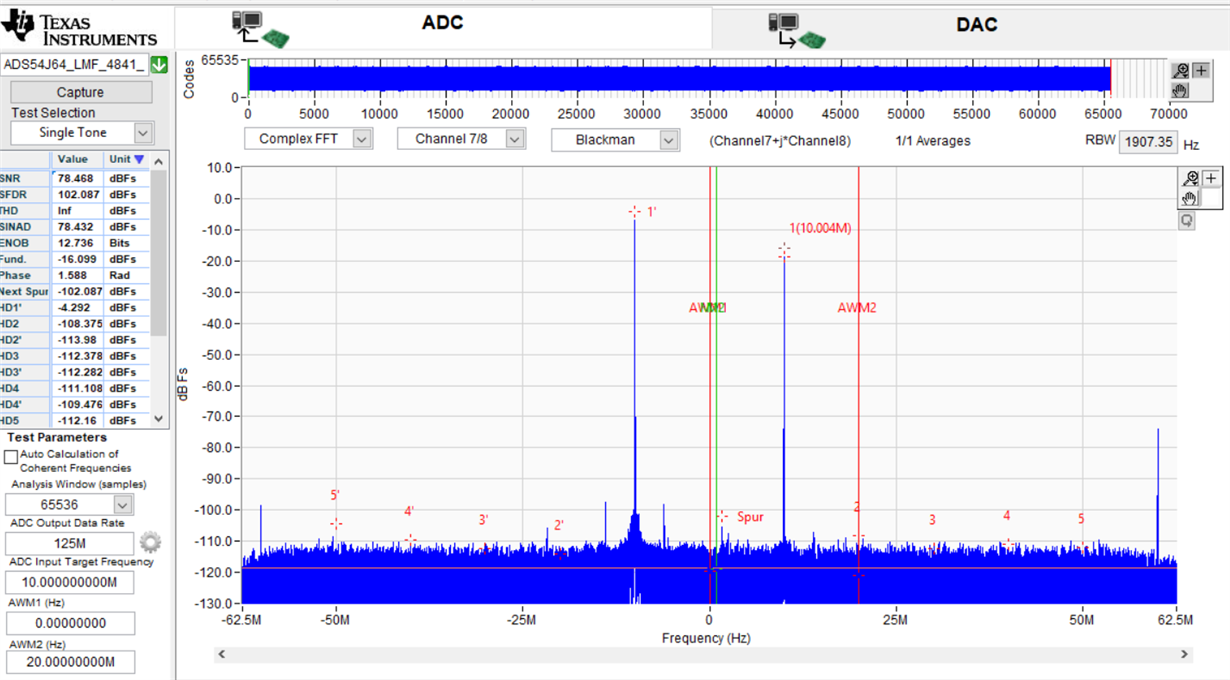

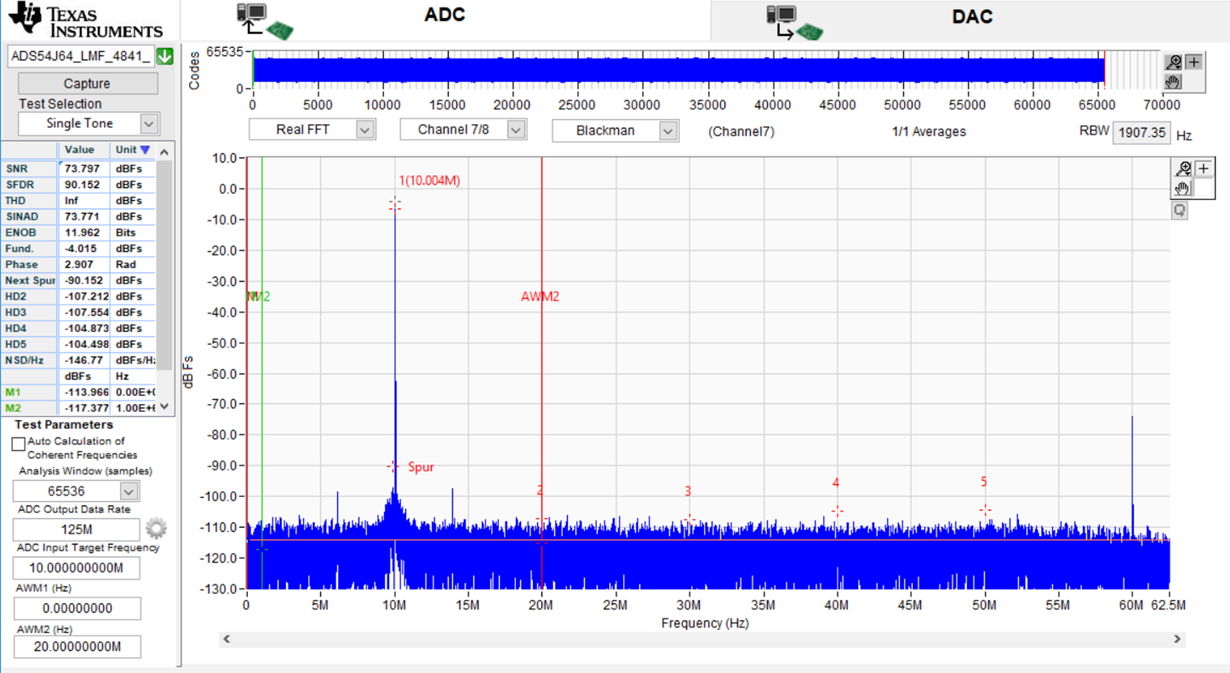

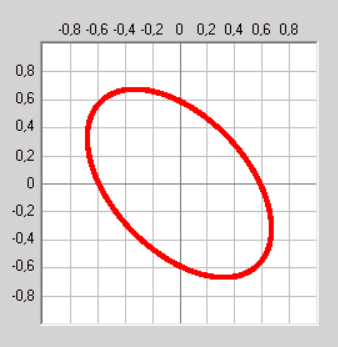

HSDC 专业版软件不支持模式6 (IQ 125MSPS)。 我们希望在具有 FMC 连接器的载板中尝试使用它。

仍然可以使用 ADS58J64 EVM GUI 设置模式6 (JP3设置为 USB 模式)吗?

我们希望在 JP3设置为 FMC 模式时绕过 CPLD。

在此配置中、CPLD 的功能是什么?

信号 FMC_D5、FMC_D6和 FMC_DIR_CONTROL 的用途是什么?

谢谢、此致

Daniel