主题中讨论的其他器件: DAC38RF82EVM、 TSW14J57EVM

大家好、

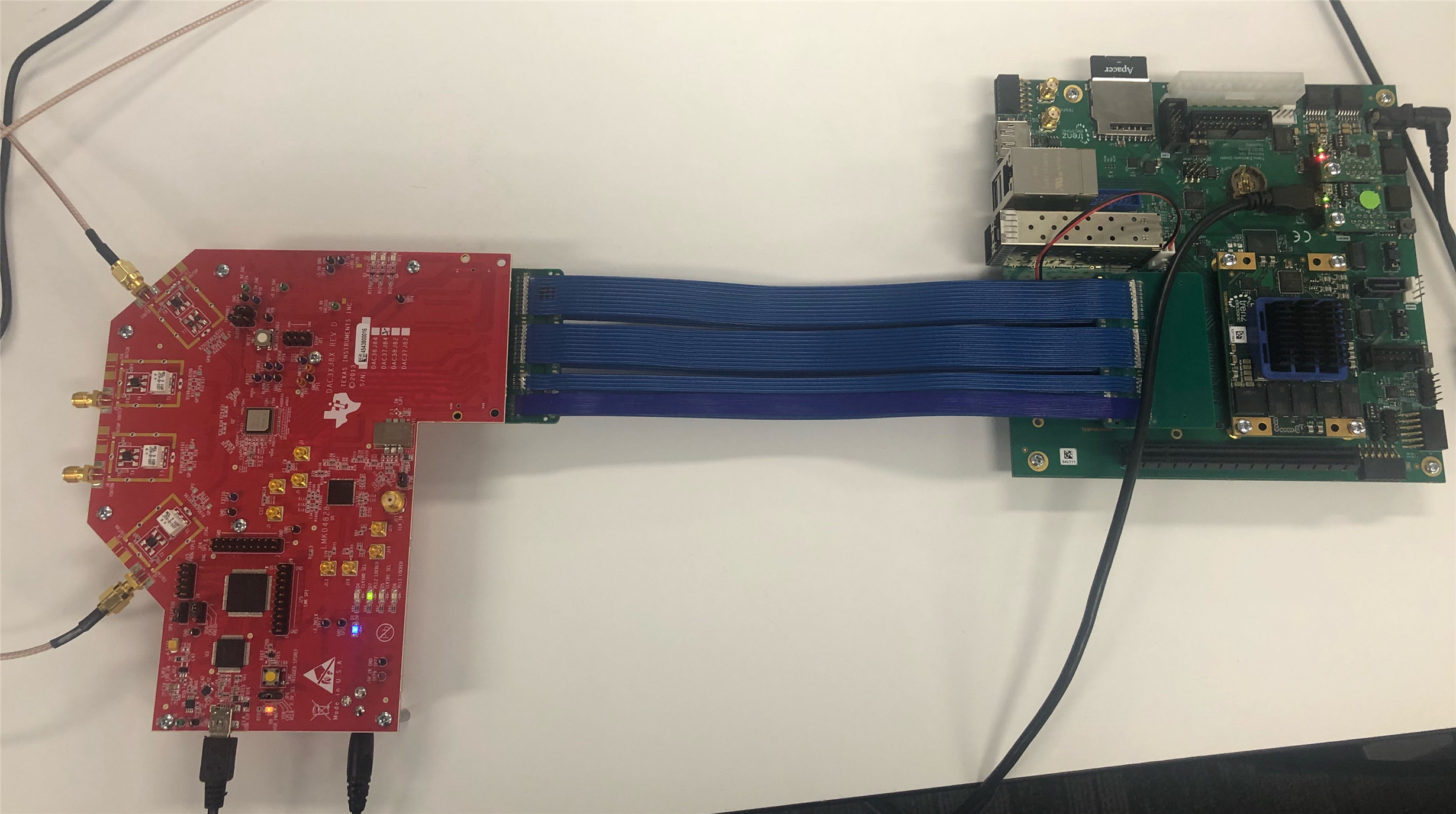

我正在尝试将 DAC37J84EVM 与 Zynq UltraScale +连接、我需要帮助

我的方法和初始设置:

L = 8

M = 4

f = 1

K = 20

S = 1

线路速率= 7.3728Gbps

基准 clk = 184.32

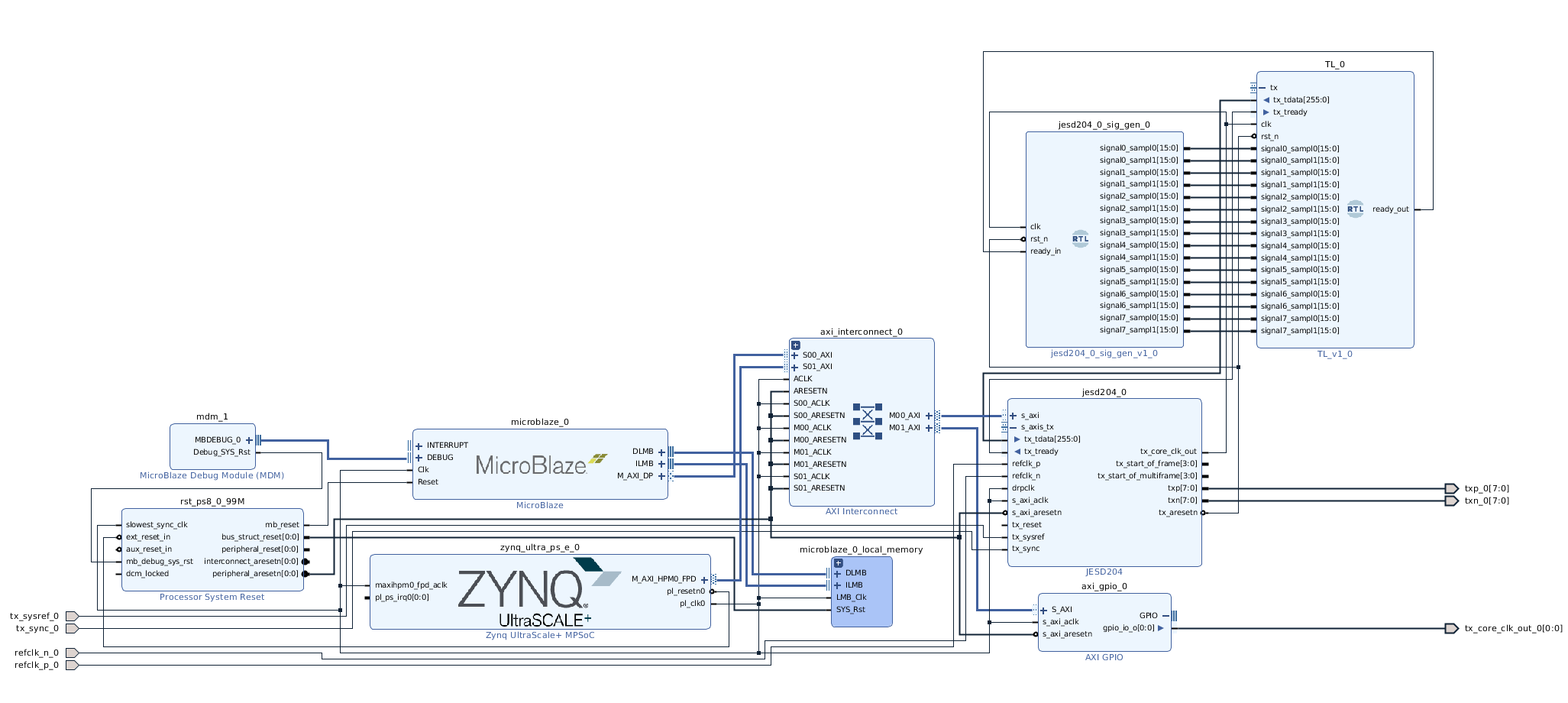

1) 1) Vivado 方框图如下所示:

所有信号/样本的数据:

分配 signal0_sampl0 ='h7530;

分配 signal0_sampl1 = 16'h0001;

2) 2)我通过 AXI 对寄存器进行编程、在 Microblaze 中配置 JESD 接口、如下所示:

XIL_Out32 (ADDR_START+0x004、0x1);//重置 IPCORE

XIL_Out32 (ADDR_START+0x008、0x1);//支持 ILA -打开

XIL_Out32 (ADDR_START+0x00C、0x0);//加扰-关闭

XIL_Out32 (ADDR_START+0x010、0x1);// Sysref -始终

XIL_Out32 (ADDR_START+0x014、0x3);// ILA 中的多帧= 4

XIL_Out32 (ADDR_START+0x018、0x0);//测试模式=正常运行

XIL_Out32 (ADDR_START+0x020、0x0);//每帧八位位组 F=1

XIL_Out32 (ADDR_START+0x024、0x13);//每多帧数 K=20

XIL_Out32 (ADDR_START+0x028、0xFF);//使用的通道= 8

XIL_Out32 (ADDR_START+0x02C、0x01);//器件子类1

XIL_Out32 (ADDR_START+0x80C、(L << 24));// L = 7 (number_of _l线道-1)、DID = 0、BID = 0

XIL_Out32 (ADDR_START+0x810、(CS << 24)|(N1 << 16)|(N << 8)| M);// CS = 0、N'= 16-1、N = 16-1、M = 4-1

XIL_Out32 (ADDR_START+0x814,(HD << 16));// CF = 0,HD = 1,S = 0,SCR = 0

XIL_Out32 (ADDR_START+0x818、0x0);// 0x818:RES1 = 0、RES2 = 0

XIL_Out32 (ADDR_START+0x004、0x1);//重置 IP 内核

注:我读回寄存器、以确保它们正确无误。

3) 3)我对 FPGA 和 Microblaze 进行编程

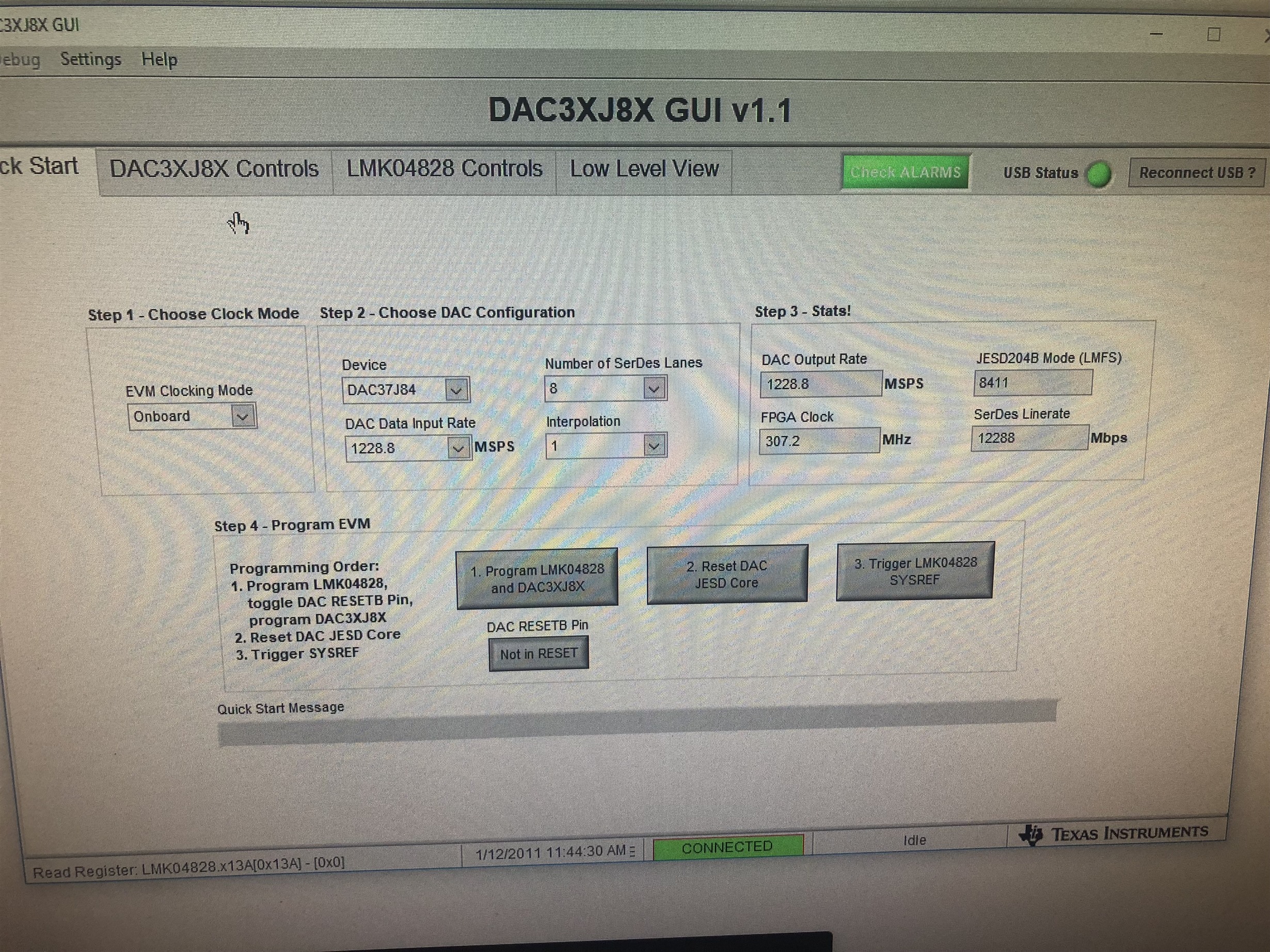

4) 4)我通过 USB 对 DAC 进行编程(DAC EVM GUI)

5) 5) I RESET JESD 和触发 sysref

6) 6)在警报窗口中、仅 DAC PLL 未锁定。 我看不到任何其他警报、在(示波器/频谱分析仪)上看不到任何东西。

我将时钟连接到 LED。 它们按预期闪烁(在时钟分频器之后)。

我不确定如何开始调试 DAC37J84EVM JESD 接口。

有什么建议吗?