主题中讨论的其他器件:ADS42JB49、 ADS54J60、 ADS42JB69EVM

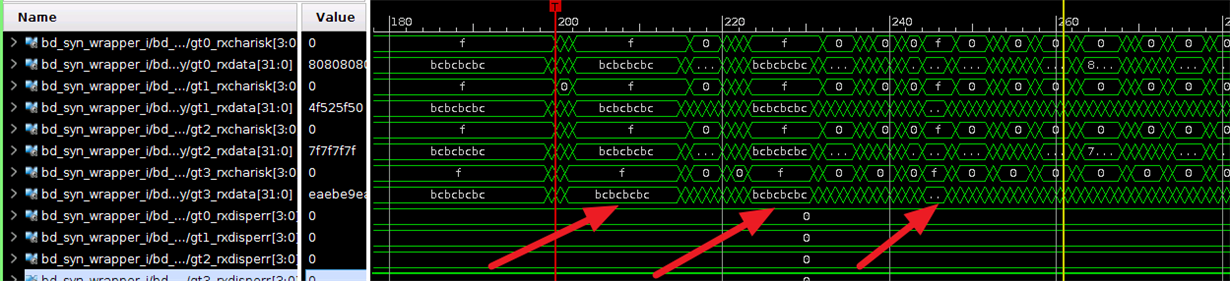

SYNC 被拉为高电平后、ILA 序列在 K28.5之后开始、如绿色 KS 所示。 然后是4K 帧、后跟正常的用户数据。

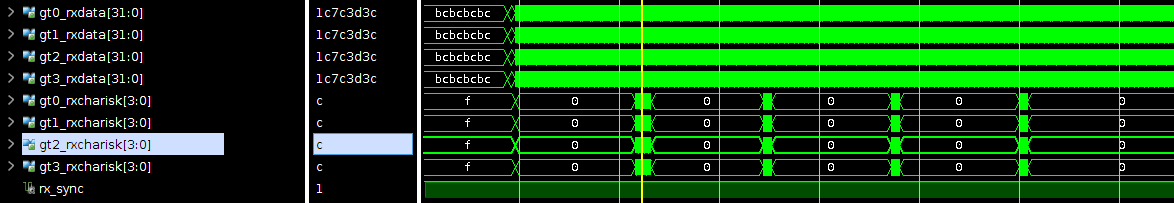

但是、该芯片250MHz、4通道、2.5Gbps、ILA 序列不能与正确的原型通信。

在国际法协会的这一进展中插入了许多 K28.5。

我们带来了最新的 EVM 板、PCB Rev D

此外、我们还测试了与 TI ADS42JB49数据表完全匹配的其他芯片、如下所示:

那么、如何解决这个问题、以满足数据表和 JESD204B 协议要求?