主题中讨论的其他器件: DAC37J82、 LMK04828

你好!

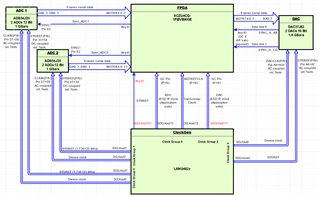

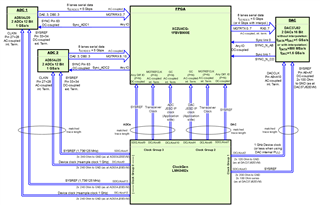

我们有一个新项目、希望通过 JESD204B 并借助 Xilinx Ultrascale+ XCZU4CG 连接两个 ADC 和一个 DAC。

我已经阅读了有关 JESD204B 的几个信息、但我仍然有一些问题、尤其是关于将时钟从 LMK0482x 连接到 FPGA 的问题。

我们目前的计划:

- MPSoC XCZU4CG-1FBVB900E

- LMK0482x PLL/时钟清除器

- 2个 ADS54J20器件(4个 ADC)

- ADC LMFS 配置8224。 因此、每个 ADS54J20器件具有8条速率为5Gbps 的通道(总共16条通道)。

1 x DAC37J82 (2个 DAC)

- JESD204B 子类1

我的问题:

-我们是否必须将"器件时钟"连接到 MGTREFCLKxP/N 或 FPGA 时钟引脚(GC、QBC)?

-我读出 SYSREF 必须连接到 FPGA 时钟引脚。 而是连接到哪个时钟引脚? 它们是否有特殊要求、例如 HP 组的 GC 或 QBC 时钟引脚、或者 HD 组上的 HDGC 时钟引脚是否正常?

- SYNC 是否需要 HP 存储块上的通用 I/O、或者 HD 存储块上的任何引脚是否正常? 它是否应该与 SYSREF 时钟位于同一个组中?

此致、