大家好、我们使用 FPGA 获取"Vout"值、有时会产生 与现实截然不同的数字值。

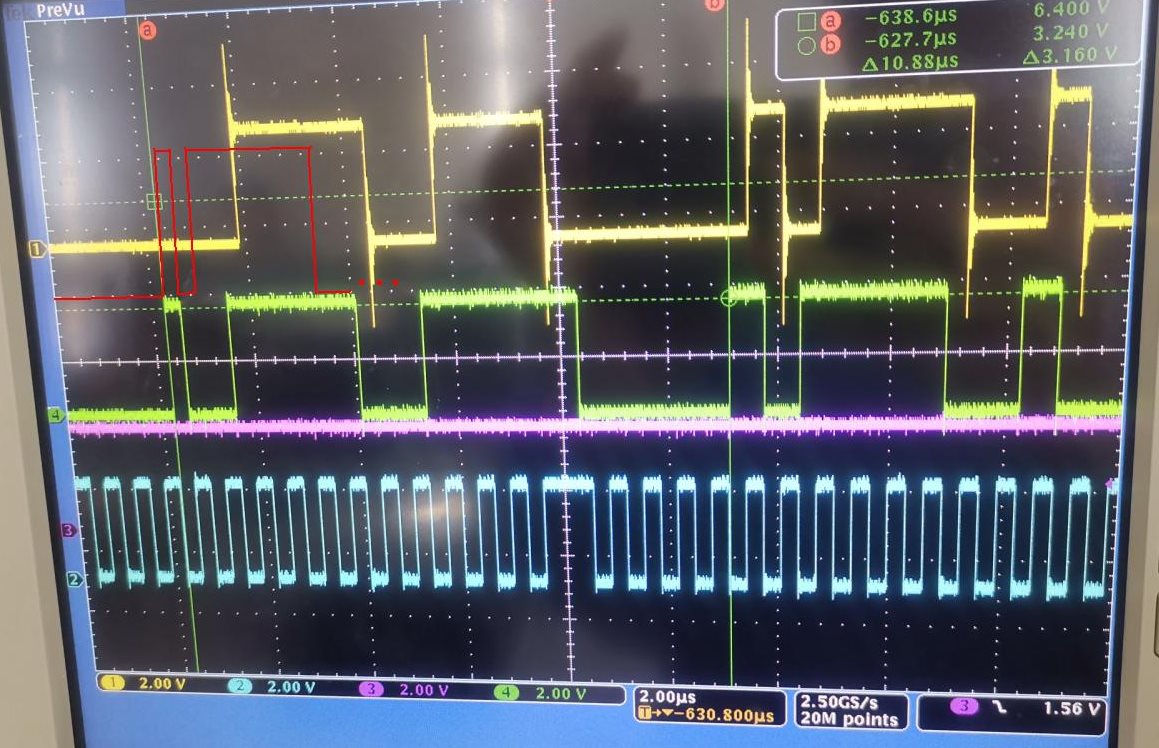

因此、我们使用示波器捕获了波形、如:

在上图中,从上到下依次为:①Data FPGA 通过 SCLK 上升沿收集的数据,④Dout μ s,③Do μ s 无关(我们用它来跟踪异常值),②SCLK μ s

两个绿色标尺在每个 DOUT 的开头标记。 从标尺 B 开始的序列是正确的、它应该是(10111...)、 在从标尺 A 开始的序列中出现了奇怪的情况、一些 DOUT 输出样本在 SCLK 的上升沿计时

首先、我们怀疑 ADC128S102在 SCLK 的上升沿误捕捉到下降沿特性、 如果是这种情况、后面的波形也会向前移动(如下图中标记的红线)、 它不会错过旁边的下降沿。 但现实情况是:高电平(1)持续半个周期、 低电平(0)持续一个半周期。

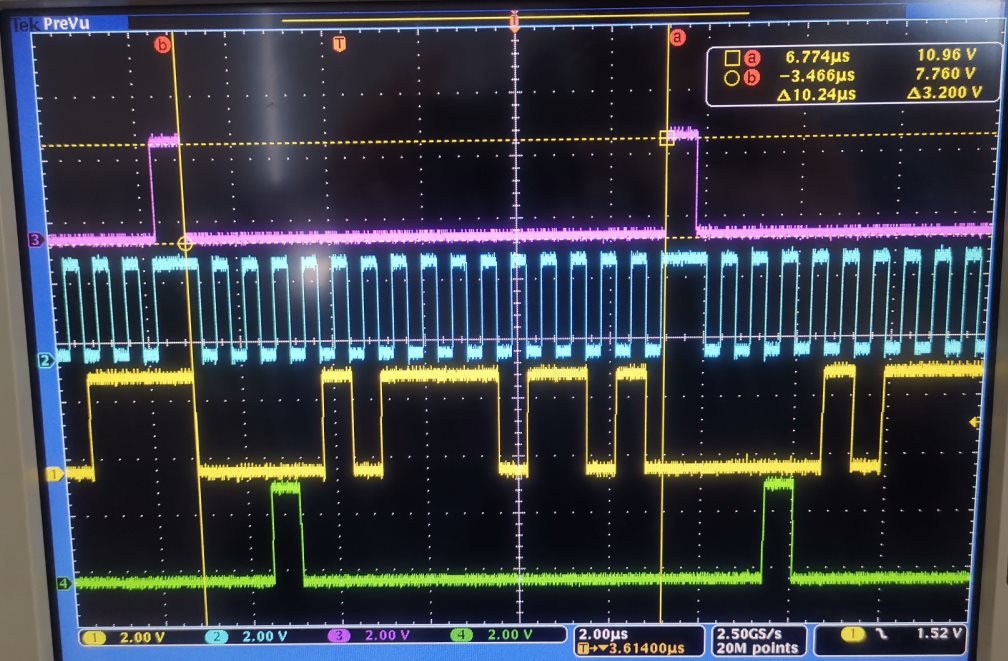

上图中未显示 CS 和 DIN 的波形、通常 AAAA 如下所示:

从上到下:CS、SCLK、DOUT、DIN

您能否就此提供解释或建议?

当前的 SCLK 频率为1.5625Mhz。 奇怪的是与此相关吗? (尽管它与奇怪相关、但也想知道发生原因)

谢谢、

Luddy