Other Parts Discussed in Thread: LMK04832, ADC34J43, ADC34J43EVM, LMK04828

主题中讨论的其他器件:LMK04832、、、 LMK04828

我计划使用 ADC34J43 + LMK04832 + FPGA 构建 DAQ 系统。 并以 ADC34J43EVM 为参考。

- 我的目标采样率为80M。 那么、进入'CLKP'的时钟和'CLKM'应该是80MHz、对吧?

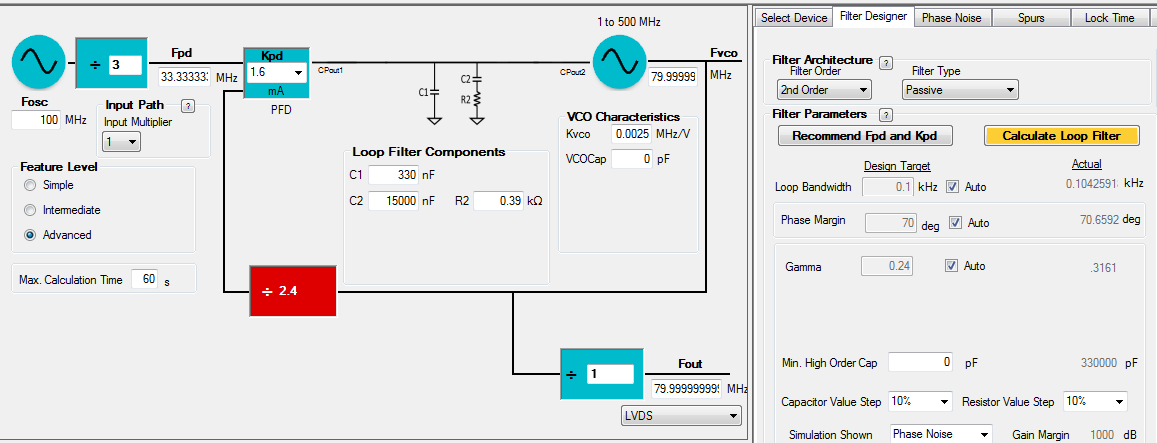

- 我发现 ADC34J43EVM 使用100MHz VCXO、因此我尝试在 PLLatinum Sim 中获取80MHz 输出、并按如下方式失败。 那么、如果我想在 这个电路板上以80MHz 的频率评估 ADC34J43、我必须启用内部分频器、对吧?

- 是否有关于如何使用 PLLatinum 的任何文档?

谢谢。