您好!

我们有兴趣购买 DAC38RF82EVM + TSW14J56捆绑包来生成脉冲、从而对光脉冲进行振幅调制(驱动 EOM)、以进行量子光学实验。 我们想知道该捆绑包是否能够生成亚纳秒(~100ps)的脉冲。 此外、我们还对捆绑包修改它能够生成的脉冲形状的能力感兴趣、例如高斯、任意以及脉冲生成是否可以在触发器上进行。

非常感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们有兴趣购买 DAC38RF82EVM + TSW14J56捆绑包来生成脉冲、从而对光脉冲进行振幅调制(驱动 EOM)、以进行量子光学实验。 我们想知道该捆绑包是否能够生成亚纳秒(~100ps)的脉冲。 此外、我们还对捆绑包修改它能够生成的脉冲形状的能力感兴趣、例如高斯、任意以及脉冲生成是否可以在触发器上进行。

非常感谢!

Jiawei、

此设置可生成的最窄脉冲为~111ps。 在单 DAC 模式下使用 DAC 时、TSW14J56EVM 的最大数据速率为9GHz、其中 LMF = 811、具有实际数据且无内插。 TSW14J56EVM 使用.csv 格式的测试数据。 关于修改脉冲的问题、这是您必须创建的内容、并作为外部测试模式加载到 TSW14J56中。 此.csv 文件是有符号整数文件、单列格式。 随附了111ps 脉冲文件的示例。

此致、

Jim

e2e.ti.com/.../3005.slwu087d.pdfJackson、

我随附的 HSDC Pro 用户指南对此进行了说明。

此致、

Jim

Jim、您好!

对迟交的答复表示歉意。 我们一直在等待这两个板到达并对它们进行测试。 我们按照 手册中的"快速入门"部分 设置了两个板、并能够在 DAC 板处于片上 PLL 模式时观察 NCO 频率(2140MHz)。

现在、我们希望电路板生成一个短路脉冲。 因此、我将包含单个高斯波形的另一个波形.csv 文件(请参阅随附的+截屏)组合在一起、并将其上传到 HSDC Pro。 由于我们的示波器只能看到高达25MHz 的频率、因此我们将 NCO 频率设置为低于25MHz 的值。 不过、我们无法从示波器观察高斯脉冲、而是观察到一些波形(请参阅图像)。 波拍内的峰值数量与 NCO 频率具有正相关关系。 这是不可取的、因为我们希望看到.csv 文件中的波形出现在示波器中。 请原谅我的无知、但我们团队中知识更丰富的成员建议将.csv 波形与 NCO 混合在一起? 我不确定如何继续。 请告知或请求提供其他信息。 大多数设置应与手册"快速入门"部分中列出的设置相同(NCO 频率和波形生成除外)。

您好、Jim、

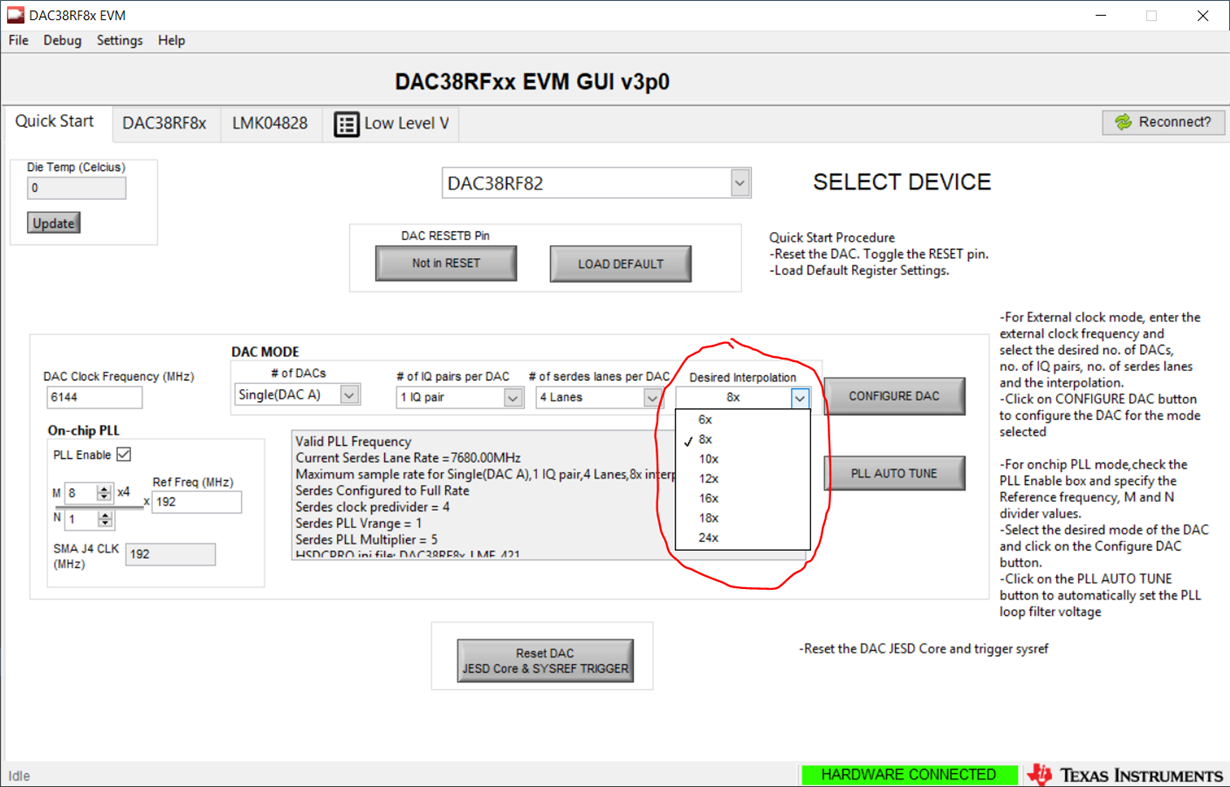

感谢您的回复! 我们一直在使用 x16插值。 通过按照建议将其更改为 x8、我们确实可以看到输出在时域中"压缩"为二倍。 但我认为我无法从 DAC 软件的"Quick Start"选项卡中获得 x4或 x2。

因此、我将尝试探索 DAC 采样率选项。 这是否意味着我需要尝试提高"DAC 时钟频率"? 由于我们没有任何 GHz 振荡器、因此我们必须将片上 PLL 与我们的 MHz 振荡器结合使用。 我发现有几个具有数字猜测的离散有效 PLL 频率。 那么、我现在的问题是:如何确定有效的 PLL 频率? 是否有详尽的列表? 我在 DAC38RF82数据表中找不到它。

再次感谢! 您的帮助使我们更接近目标。

Jiawei

e2e.ti.com/.../3276.PLL-setup-example.pdfJiawei、

请参阅随附的文档是否对此有所帮助。

此致、

Jim

e2e.ti.com/.../5722.DAC38J84-Clock_2C00_-PLL-and-SERDES-Configuration.docxJiawei、

可用频率由两个内部 VCO、外部基准和 PLL 使用的分频器的范围决定。 请参阅随附的文档、了解有关此内容的更多信息。

此致、

Jim

e2e.ti.com/.../4035.DAC38J84-Clock_2C00_-PLL-and-SERDES-Configuration.docxJiawei、

随附的文档应有助于解决您的 PLL 频率问题。

此致、

Jim