主题中讨论的其他器件: SN74AUC1G74

您好!

我正在调试一个由四个 ADS1675组成的 DAQ 系统、这四个 ADS1675预计会同时采样和输出数据、但不会。 我测量 DRDY 的到达时间偏差约为10。 100纳秒。 这些器件配置为高速 LVDS 模式、并以4MSPS 的全速连续运行。 输出数据正确(对应于模拟输入)。

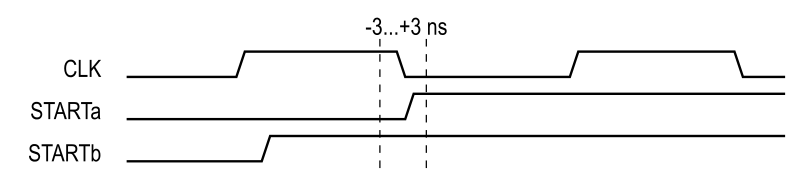

START 同步到 CLK 的下降沿、并在保持高电平之前脉冲3个 CLK 周期。

在数据表(SBAS416D)的时序要求下:高速 LVDS 第7页是符号 tSTCLK 的设置要求、给出时间为-3..3ns。 如何理解最长设置时间?

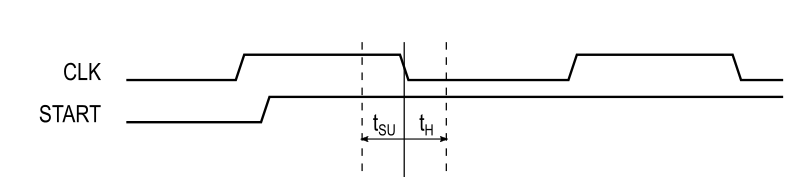

2.在时序要求下:从第9页开始是一个到给定上升沿的最小建立时间0.5 tCLK、这与第1点相反。

您是否知道数据输出为何不是同步的? 多个同步的 ADS1675之间的 DRDY 输出时间可实现或典型偏差是多少?

此致。