主题中讨论的其他器件: DAC38RF80、 LMK04828、 LMX2582、 TIDA-01021、 LMX2594

尊敬的 TI:

我们在设计中使用了三个 ADC12DJ3200和三个 DAC38RF80。

ADC 和 DAC 将有单独的 PCB。

我们使用 LMX2582和 LMK04828为三个 ADC/DAC 和 FPGA 计时。 我们希望同步所有三个 ADC/DAC、并且还希望为每次电路板上电/断电实现确定性延迟。

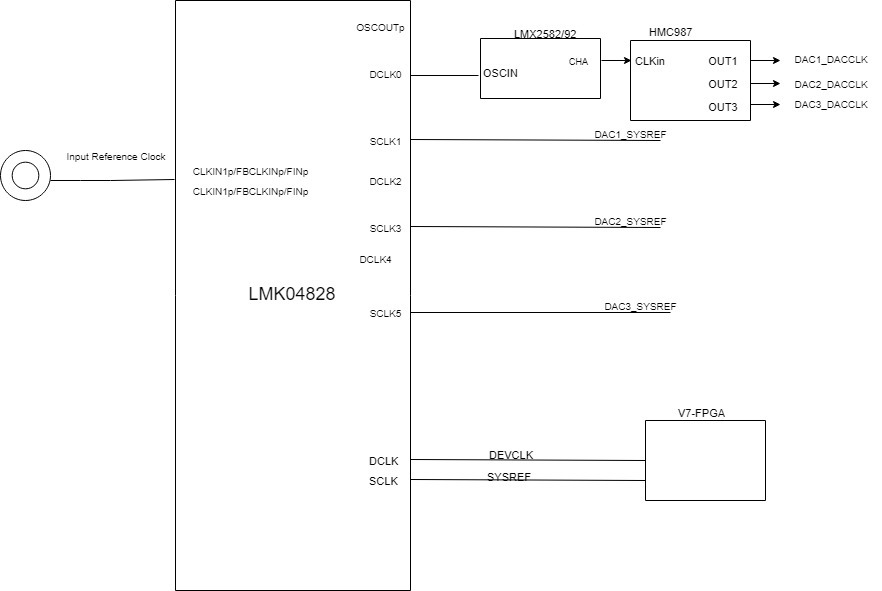

我们的 ADC 和 DAC 时钟方案相同、如下所示:

现在我们知道、为了实现 ADC/DAC 的确定性延迟和同步、我们需要使用 SYSREF 在 ADC/DAC 和 FPGA 中生成 LMFC。

但为此、建议使用同一器件生成 SYSREF 和 DEVCLK、但在我们的情况下、SYSREF 是从 LMK04828生成的、而 DEVCLK 是从 LMX2582生成的、用于 ADC 和 DAC。

即使我们尝试长度匹配 SYSREF 和 DEVCLK、由于 DEVCLK 来自 LMX2582、并且 LMX2582的锁定时间会因电路板每次上电而异、SYSREF 也来自 LMK04828、 然后、如何确保 SYSREF 在每个下电上电时满足设置和保持时间关断 DEVCLK。

假设在首次上电时,SYSREF 不符合设置保持时间 wrt DEVCLK,然后我们提供从 LMK04828到 SYSREF 的延迟,以满足设置保持时间。

但是、当我们对电路板进行下电上电时、LMX2582或 LMK04828的锁定时间可能与上一次下电上电时不同、那么我们可能需要再次调整 LMK04828的延迟以满足设置保持时间要求。

但我们无法针对每个下电上电周期执行该操作、对吧?

那么、我的问题是如何使用我们的电流时钟方案(附带方框图)实现三个 ADC、DAC 的确定性延迟和同步?

请帮帮我们。

我们将非常感谢尽早作出反应。

谢谢、

Lalit