主题中讨论的其他器件: DAC37J84、 DAC38J84

您好!

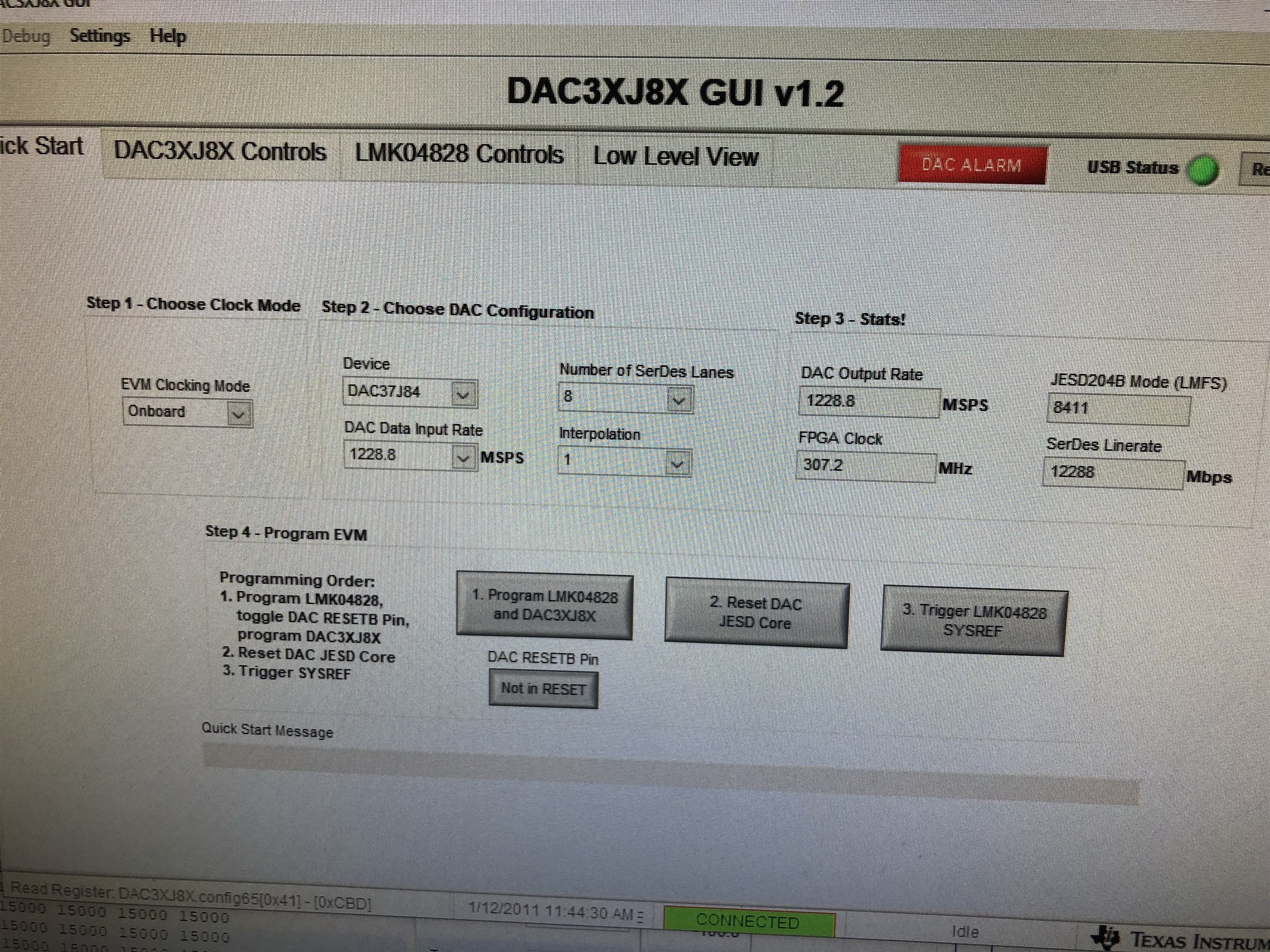

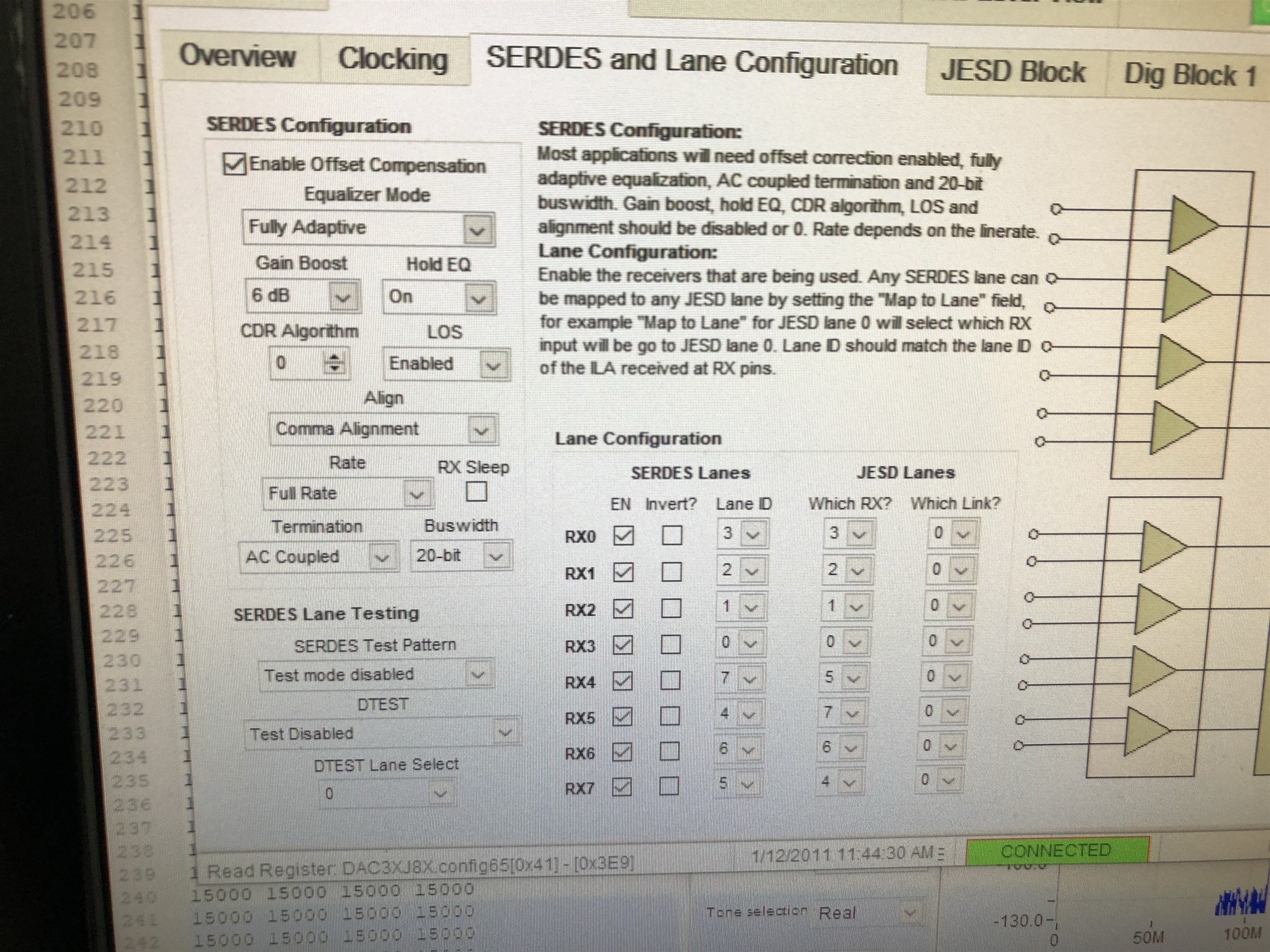

我在 TSW14J56和 DAC37J84EVM 之间运行12.288GB JESD 链路(换序关闭)。

不过、我可以看到数据、DAC GUI 显示 发生了大量8b/10b 错误、并且没有对齐错误。 大量错误会导致链路重新同步、并且输出波形将 在重新同步期间消失。

此外、我注意 到、在换序时、我得到的 错误数减少了8b/10b (0-5000并且缓慢增加)、但 对齐错误数增加(总体链接0错误计数小于未换序的错误数)。

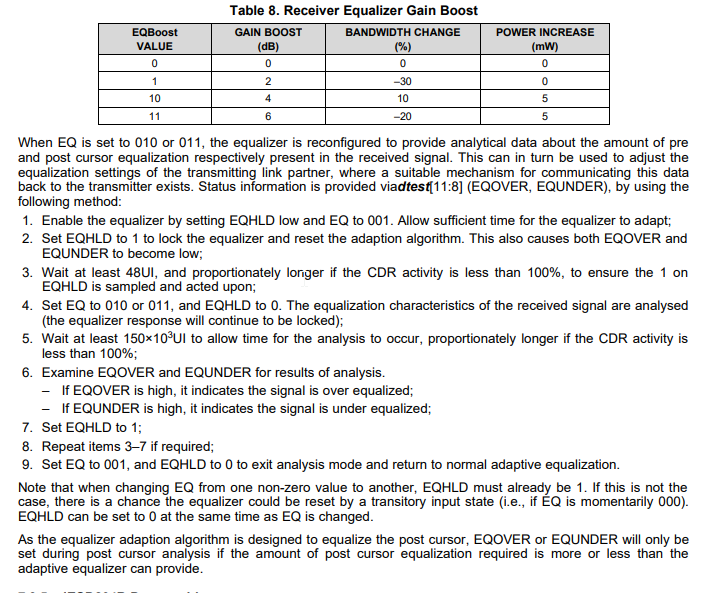

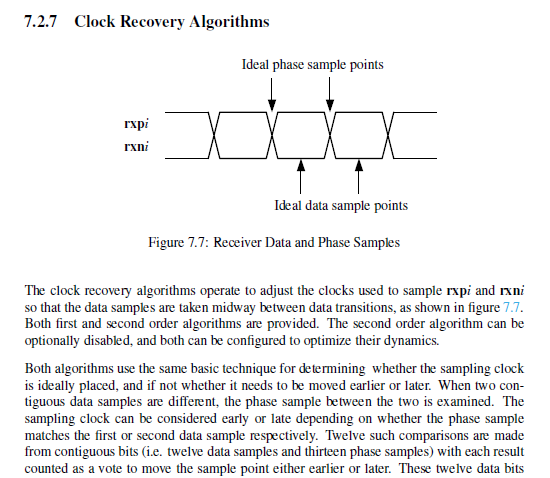

1) 1)在定制构建板上、可以采取哪些措施来改进 BER?

2) 2)从数据表中、不清楚如何使用眼图扫描。 我需要 JTAG 吗? 这可以通过 SPI 实现吗?

3) 3)我是否需要其他软件来运行眼图扫描?

谢谢、

安东