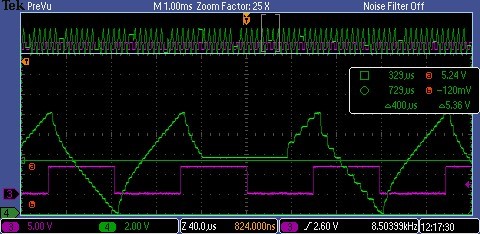

我的设计使用前4个通道作为任意波形发生器、以400kHz 更新速率(50MHz SPI)运行、然后同步更新它们。 其余四个 DAC 用作可随时更新的实用 DAC。 我的 RTL 设计对前4个通道使用流模式、然后在前4个 DAC 进行流处理后、针对4个实用程序插槽中的一个插槽对通道更新进行插槽更新。 但是、在对 DAC 1-4进行流式传输、然后发出 LDACn 选通脉冲后、如果下一个 DAC 是 DAC5、我会遇到问题。 其他3个工作正常。 在流选择之后、LDACn 与选择下一个连续 DAC 之间是否存在时序关系 sip?

同样、我的序列是:

1) 1) CS 低电平

2) 72位传输- DAC1_ADDR (8位)、DAC1_DATA (16位)、DAC3_DATA (16位)、DAC3_DATA (16位)、DAC3_DATA (16位)、DAC4_DATA (16位)

3) 3) CS 高电平

4) 4) 20ns 延迟

5) 5) LDACn 选通信号20ns

6) 6) 15ns 延迟

7) CSn 为低电平