您好!

我想确认串行接口,您能给我一些意见吗?

问题1.

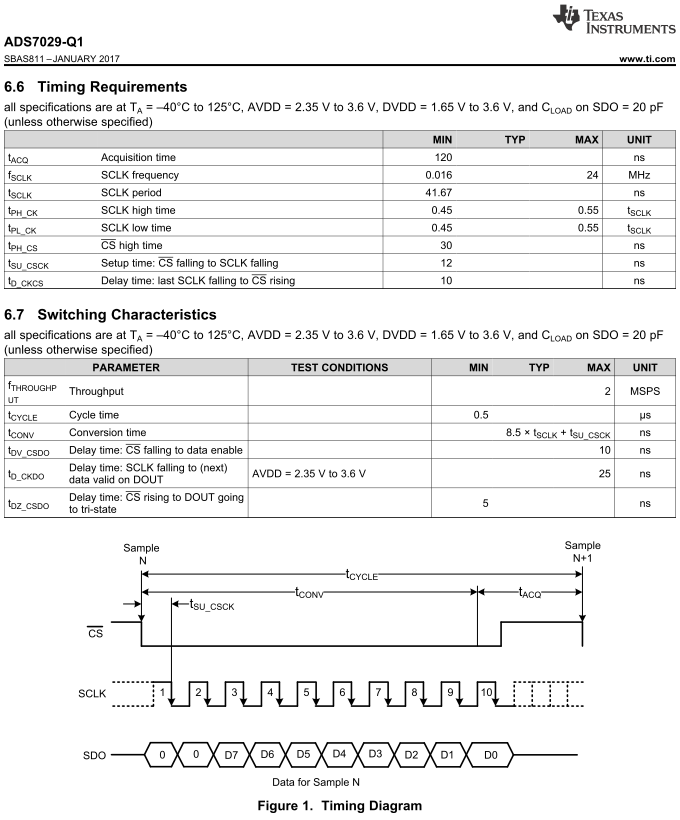

我的理解是否正确,即当/CS 下降时 SDO 变为“0”,SDO 保持“0”直到 SCLK 下降?

问题2.

我的理解是否正确,即在使用 FPGA 采集数据时使用 SCLK 的上升沿,因为在/CS 信号下降后 SDO 数据与 SCLK 的下降沿同步切换?

问题3.

我的理解是否正确,即2位的零数据总是作为虚拟位添加到输出数据中?

问题4.

我的理解是否正确,即 SDO 的 D0在 SCLK 的第9个下降沿输出?

问题5.

即使第10个 SCLK 下降,SDO 是否仍保持 D0?

问题6.

即使第11个 SCLK 下降,SDO 是否仍保持 D0?

问题7.

D0是否保持直至/CS 变为高电平?

问题8.

当/CS 为低电平时 SCLK 是否能保持高电平?

此致、

加藤