您好!

我的应用需要通过 FPGA 从四个 ADC3444采集样本。 我对 ADC 的同步性以及是否可以通过时间关联样本有一些顾虑。

四个 ADC 中的每一个都接收相同的125MHz 采样时钟、并将以两线制模式运行。 如何确保每个 ADC 的转换同步? 同样、每个 ADC DCLK 和 FCLK 之间的最坏情况相位差是什么、这是否会导致 FPGA 中每个 ADC 的样本的时间相关性出现问题? 是否可以利用 SYSREF 引脚来确保数据的同步?

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我的应用需要通过 FPGA 从四个 ADC3444采集样本。 我对 ADC 的同步性以及是否可以通过时间关联样本有一些顾虑。

四个 ADC 中的每一个都接收相同的125MHz 采样时钟、并将以两线制模式运行。 如何确保每个 ADC 的转换同步? 同样、每个 ADC DCLK 和 FCLK 之间的最坏情况相位差是什么、这是否会导致 FPGA 中每个 ADC 的样本的时间相关性出现问题? 是否可以利用 SYSREF 引脚来确保数据的同步?

谢谢你。

Amy、感谢您的回答、

也许我对您的理解不正确。 四个 ADC 中的每一个都将接收非常相同的125MHz 采样时钟。 这些布线的长度是匹配的、因此任何一对 ADC 之间都不应存在采样时钟偏差。 这应该会同步 ADC 转换、但我不相信这会同步每个 ADC 的 LVDS 信号。 您能否澄清一下您的意思 :"您可以使用生成至少4个相位对齐频率的时钟源作为系统基准输入"。 为什么 SYSREF 需要第二个时钟? 只需脉冲一次 SYSREF 引脚即可同步 ADC LVDS 信号是否还不够? 如果需要第二个时钟,如果我打算以125MSPS 的全速率进行采样,那么它的频率应该是多少?

谢谢

Amy、

该部件有两个时钟输入。 CLK 和 SYSREF。 CLK 是采样时钟输入。 当我说 四个 ADC 中的每一个都将接收长度匹配的125MHz 采样时钟时、我将描述这一信号。 我知道您正在讨论 SYSREF 输入、并且每个 ADC 也应该使其 SYSREF 布线长度匹配、但我想了解 您描述的第二个时钟为何对我的应用是必要的。 为什么我需要对每个 ADC 的 SYSREF 引脚应用第二个时钟、而不是只对该引脚应用一个低-高转换?

作为参考,我将查看此版本数据表的第50页: ADC344x 四通道、14位、25MSPS 至125MSPS 模数转换器数据表(修订版 B)(TI.com)

此致

Adam、

唯一会使 FCLK 偏斜的是 ADC 采样时钟加上器件之间高达几百 ps 的孔径延迟变化。

正如 Amy 提到的、如果不在 ADC 内使用2分频或4分频选项、则无需 SYSREF 输入。 SYSREF 的名称有点令人困惑 、因为它通常是指 JESD 接口器件的系统参考。 在该器件中、SYSREF 反映了其他 LVDS 器件中通常称为选通的功能、通常用于在每个内部转换器的高通道数器件中对齐采样时钟。 不管怎样、这一点都不重要、只是希望稍微清除一下这个命名规则、因为它过去给我们的一些客户造成了困惑。

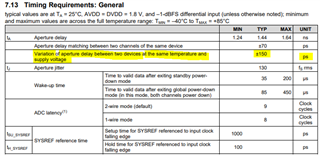

该器件内唯一的不确定性是孔径偏斜(孔径延迟)、TI 保证在给定系统中任意数量的器件之间在任一方向上均小于150ps (即总偏斜< 300ps)。 假设这是125MSPS 器件、一个时钟的周期为8ns。 这意味着 FCLK 将在所有器件上与相同的时钟边沿对齐(前提是采样时钟确实是相位对齐的)。 这也意味着 FCLK 之间的总变化量应小于300ps。 该值应足够低、以便 FPGA 可以在接收器中随意摆动、除了设置/保持时序之外、不会出现任何问题。

关键因素是系统中所有器件的采样时钟对齐和布线长度匹配、以及每个器件的 DCLK 和 FCLK 长度匹配。 由于 FCLK 将进行相位校准、因此只需将一个 FCLK 接入 FPGA 即可实现同步、但许多客户仍会将 FCLK 从所有器件路由到其 FPGA、作为安全措施。

希望这有助于澄清一些问题。

此致、Chase

Adam、

我的错误、您回答正确。 数据表似乎表明、FCLK 在1线模式下可能具有高达3.7ns (6.5ns-2.7ns)的偏斜(最坏情况下)、 在2线模式下可能具有高达6.42ns (0.44*TS (8ns)+Δtdelay Ω(2.9ns))的偏斜。

不过、这将表示器件间的差异可能会超过3个 DCLK 周期(或由于 DDR 而导致高达6位的数据)。 请允许我们就此与我们的设计团队进行核实。 请注意、对于假日周、响应可能需要一段时间。

此致、Chase

Adam、

我与我们的一位更熟悉此器件的工程师进行了简短的讨论。 DCLK 与 FCLK 对齐以确保建立/保持时序窗口。 我上面提到的 tPDI 值不正确。 FCLK 和 DCLK 将从采样时钟延迟3.5ns ( 0.44*TS = 8ns)固定值。 Δ 的变化只是延迟时间 Δ t tDELAY 的变化、即5.9ns - 3ns ≅2.9ns 的器件间最坏情况偏斜。 Δ 该 Δ t tDELAY 是 Δ Δ tPDI 的唯一可变因子,因此 Δ t tPDI 仅 为2.9ns (前提是输入采样时钟同相)。 我们建议对每个 FCLK 进行布线并用于对齐特定转换器的数据。 很抱歉、我之前有任何困惑。 我们正在尽最大努力、而许多工程师都在外出度假。 祝您感恩节愉快。

此致、Chase