主题中讨论的其他器件:LMK04828、 ADC32RF45

我的设计有一个麻烦的问题。 我有一个由 LMK04828驱动的 DAC38j84、正如在 DAC38J84评估板上完成的那样。 我使用冷冻机122.88 MHz 振荡器作为参考。 我看到的是、当我的 JESD 通道运行时、DAC 时钟上的 SSB 相位噪声增加(通过查看备用 LMK 输出可以看出)。 我已经将我的布局与评估板进行了比较、除了我在 sysref 行上没有看起来像衰减器的内容外、没有任何明显的东西。 请参见随附的图像。

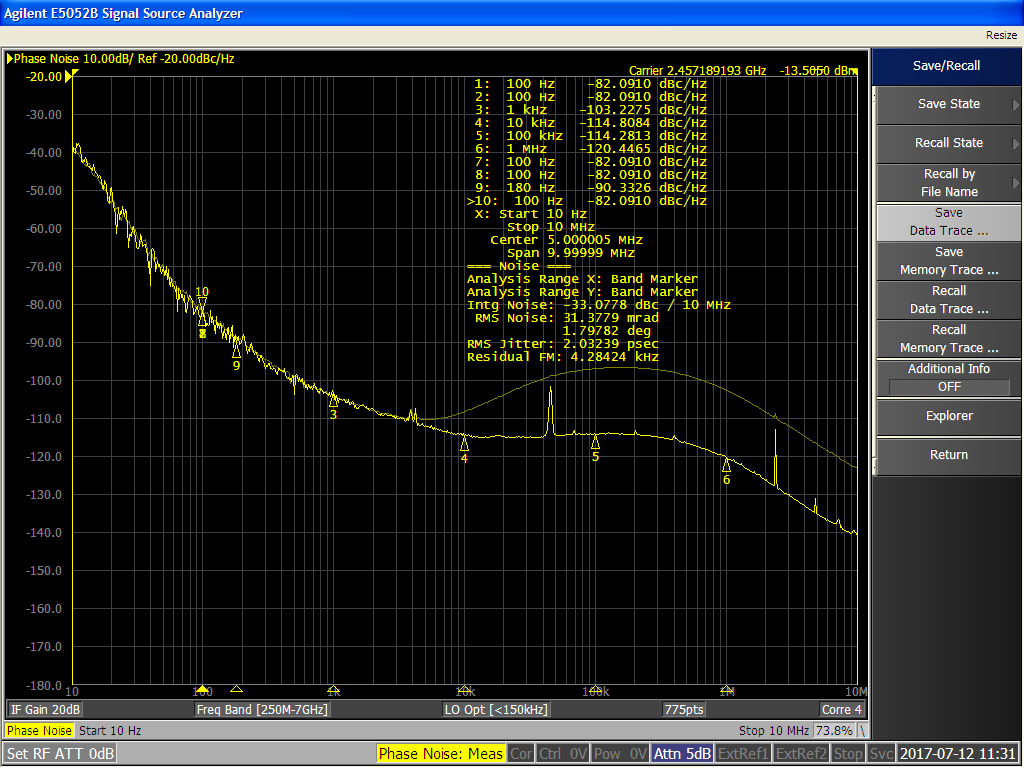

没有有关此电路的文档、我想知道它是否在 DAC 和 LMK 之间提供了某种程度的隔离? 还有其他人可以考虑我的 JESD 通道如何影响 LMK DCLK 输出上的相位噪声吗? 您可以在下面看到我要讨论的内容。 亮黄色迹线是 ~2457.6MHz 时的 DCLK6输出。 较深的黄色迹线是 JESD 通道打开且扰频器激活时的 SSB 相位噪声。 如果我关闭扰频器、我会看到离散边带。

我的设置是在 DDC NCO 设置为450MHz 时使用4倍插值。 复杂 IQ 信号的 DAC 速率为2457.6MHz。