Other Parts Discussed in Thread: ADS1256, OPA350, TPS7A47, ADS1261, ADS131E08

主题中讨论的其他器件: REF5025、 OPA350、 TPS7A47、 ADS1261、 ADS131E08

您好!

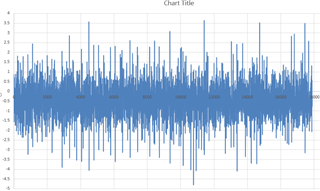

我正在使用 Verilog 代码处理 ADS1256。 我正在连续模式下读取转换后的数据。 电流设置为连接三个差分通道并保持断开状态。 问题是、我在所有三个通道上都在有负载和无负载的情况下在输出端发现噪声干扰。 我甚至尝试缩短其中一个差分通道的输入(即0V)。 问题未变。 这在该 ADC 中是常见的情况吗? I 之后的操作序列为:SELFCAL (加电后)、 SDATAC、STATUS、ADCON、DRATE、 IO_REG、SELFCAL、MUX、RDATAC (带环回)。 DREADY 符合我设置的 DRATE。 我甚至确保 SCLK 上没有干扰。 主时钟频率为7.68MHz、SCLK 频率为~1MHz。 我附加的其中一个图像用于参考其中一个差分通道。 对于 PGA 64、它处于 DRATE 3750SPS。

我尝试了100、500、1000、3750、7000的数据速率、 15000SPS、PGA 64、32、8。 问题是相同的。 ADC 中是否存在任何限制? 我希望该设计在 PGA 64和 DRATE 3750SPS 下工作。 根据数据表、确保满足原理图要求。 您能帮我解决输出端的这个噪声吗?

谢谢