主题中讨论的其他器件: ADS6444

团队、

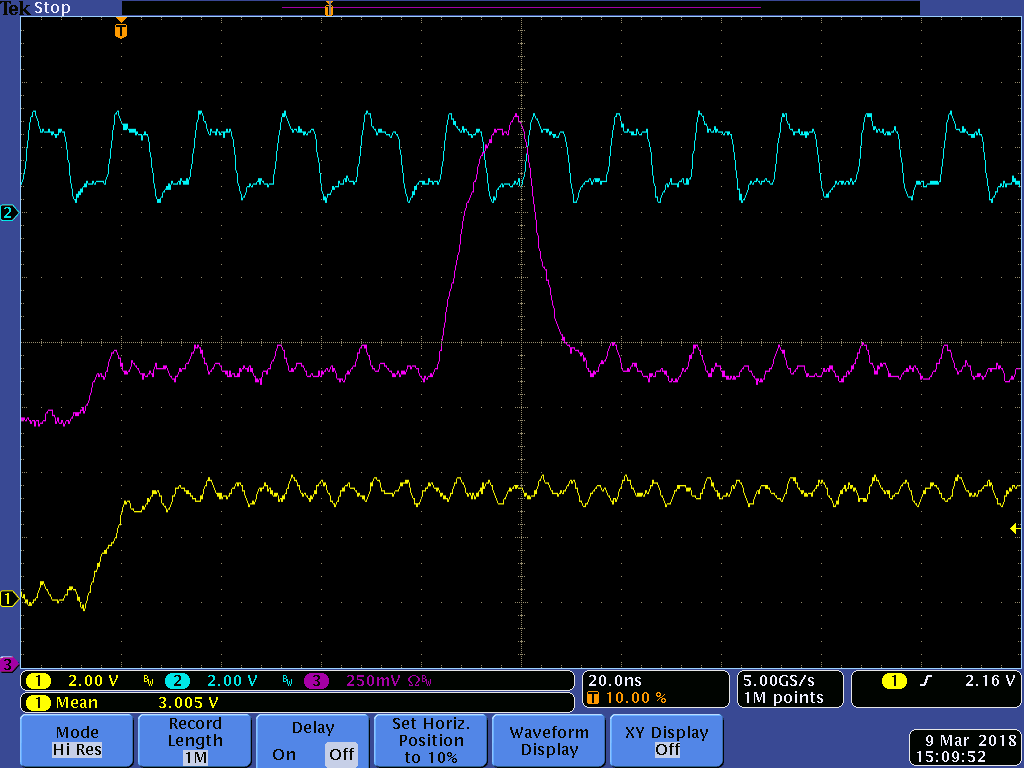

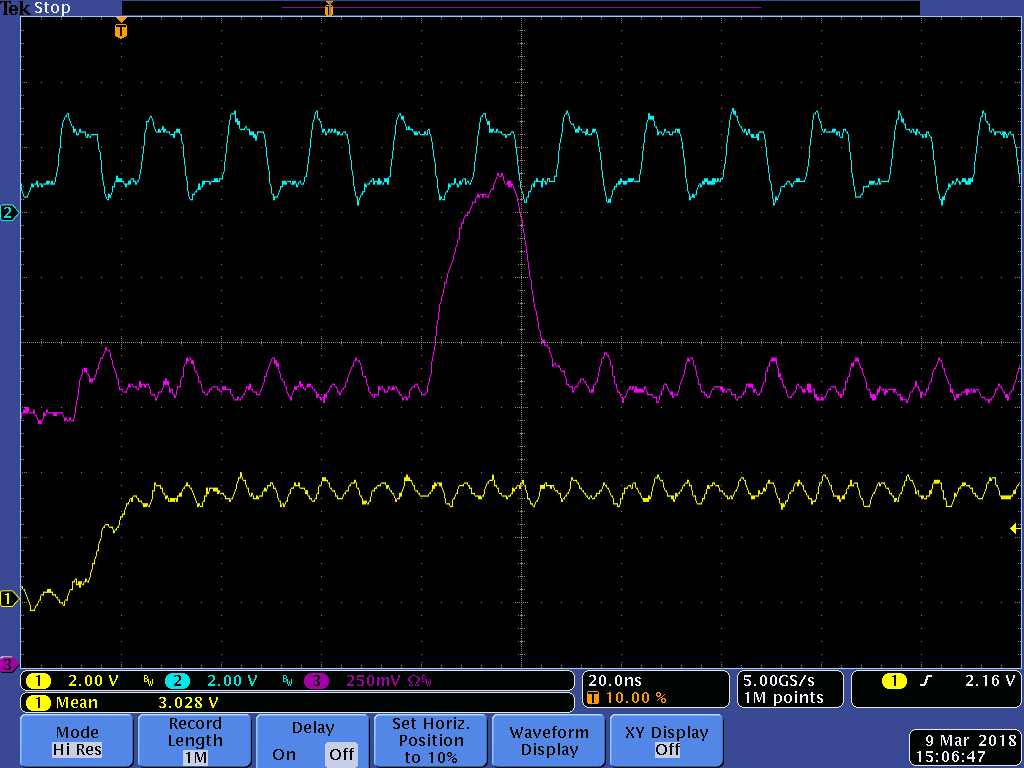

在自定义系统启动期间、对于给定的模拟输入、ADC3443的数字化输出不符合预期。

您能否确认采样是否在输入时钟的上升和下降上完成?

SBAS670B 的图141说明了采样是在下降沿完成的。 正确吗?

http://www.ti.com/product/ADC3443/datasheet/parameter-measurement-information#SBAS6703708

模拟输入信号上的稳定时间/延迟是多少?

提前感谢您的帮助。

Anthony