Other Parts Discussed in Thread: DAC084S085

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC084S085 您好!

SPI 规范

关于 DAC084S085上的 SPI 说明、我的客户提出了一个问题。

(问题)

(1)

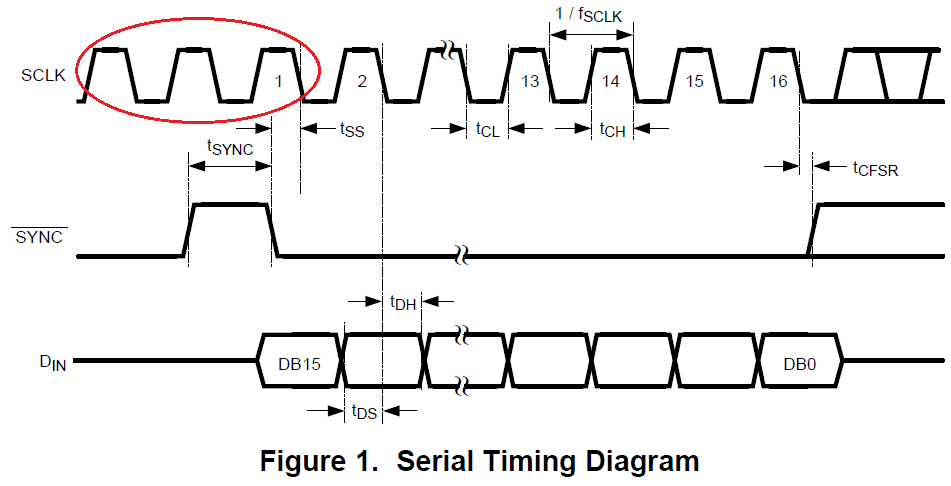

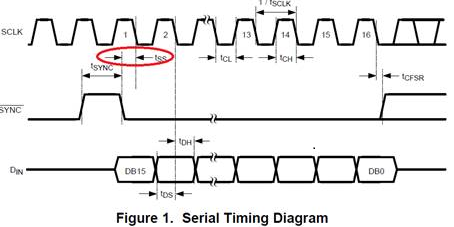

根据图1 (数据表第6页)、SCLK 在同步脉冲之前被输入。

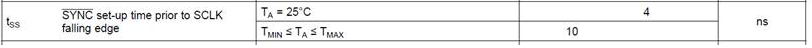

同步脉冲之前是否需要 SCLK?

我知道、通常在 CS (SYNC)下降沿之后输入 SPI SCLK。

(2)

关于 SPI 模式(CPOL/CHA)、

DAC084S085支持哪种模式?

我认为图1中的 SPI 模式为 mode1 (CPHA=1/CPOL=0)。

我的理解是正确的?

此致、

TAO 2199