大家好、

您能告诉我哪种 SPI 模式可以支持吗? (在主侧)

在我的理解中、仅 MODE0支持、但请告诉我其他模式是否支持。

谢谢你。

此致、

Jade

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Jade、

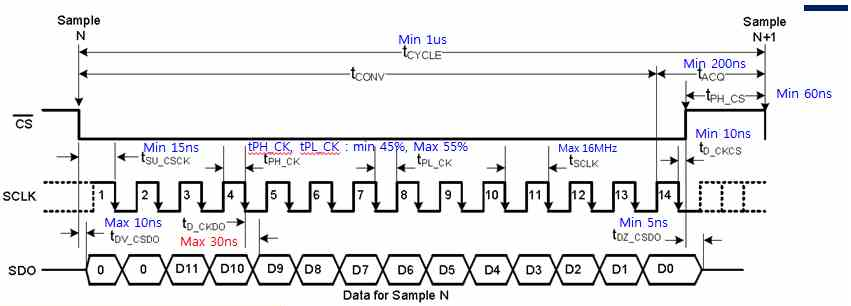

在典型运行条件下、由于 DOUT 上的数据在下降沿发生变化并在下一个上升沿被捕捉、这可被视为主机的模式0运行。 但情况并非总是如此。

假设 ADS7042在16MHz 的最大 SCLK 下运行(62.5ns 时钟周期)、AVDD 下限范围为1.65V 至1.8V。 根据数据表第8.6节中的时序特性、SCLK 下降至 DOUT 有效延迟可高达50ns。 缓冲器和大迹线电容会进一步延迟该信号。 在这种情况下、需要在模式1下操作主机并在 SCLK 的下一个下降沿捕获数据。

因此、主机的 SPI 模式选择取决于特定设计的运行条件。

此致、

Sandeep

您好、Sandeep、

客户使用 AVDD=3.3V。 在本例中、仅支持模式0?

1、下降沿发生数据变化、您是否会告诉我从下降沿开始的最小数据保持时序? TD_CKDO 是更改数据的最大延迟。

您是否会告诉我最小 tHOLD 规格?

2.从下降沿开始、如果客户满足了主机请求的足够的保持时间、它看起来像是支持所有 MODE0~3、对吧?

供参考、它们的主设置如下:

IPQ8069主设备设置

- SPI 时钟8MHz

访问间隔:最小300ns

支持的 SPI 模式#1:模式0

时钟极性(CPOL):0

时钟相位(CPHA):0

=>主 MISO:在上升沿被捕捉

支持的 SPI 模式#2:模式3

时钟极性(CPOL):1.

时钟相位(CPHA):1.

=>主 MISO:在上升沿被捕捉

支持的 SPI 模式3:模式1

时钟极性(CPOL):0

时钟相位(CPHA):1.

=>主 MISO:在下降沿捕捉

(保证保持时间:CAD 路由延迟+最小 TD_CKDO[Unkown ])

支持的 SPI 模式4:模式2

时钟极性(CPOL):1.

时钟相位(CPHA):0

=>主 MISO:在下降沿捕捉

(保证保持时间:CAD 路由延迟+最小 TD_CKDO[Unkown ])

谢谢你。

此致、

Jade