您好!

我的客户目前正在使用 ADS7853进行设计、他们有问题。

首先,他们将配置寄存器设置为16位模式,2条数据线路等数据:“1000_101010_0001_0000”

测试时钟频率为2.5MHz、从10MHz 开始、这正是他们将在产品中使用的频率。

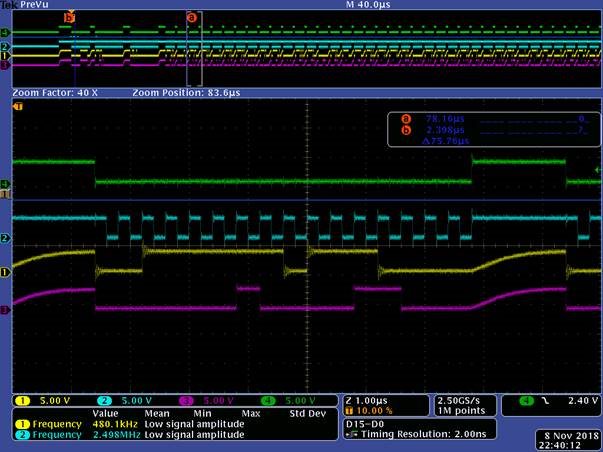

绿色:CS_n

数字1:SDI

蓝色:SCLK

黄色:SDOA

紫色:SDOB

接下来、他们初始化已配置值的读数:

然后、它们读取配置的值(在这里、输出数据显然是在 SCLK 的下降沿启动的):

最后,他们输入了“运行时”,经常在其中读取值。

在这里、您可以看到数据是在 SCLK 的上升沿启动的。 数据表指出、数据应在下降沿启动。

请参阅数据表中的第42页和第43页。 在 CS_n 变为低电平后、应在第二个下降 SCLK 上输出 D11。

我在数据表中找不到应该在上升沿启动数据的任何地方,但是在第41页,数据在图表中看起来是这样的,但是文本和表格显示的是下降沿。

请在此处帮助我们。

此致、

Stani