主题中讨论的其他器件: DAC38RF80

大家好、

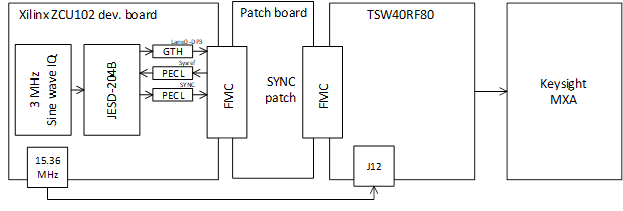

我们对连接到 Xilinx ZCU102评估板的 TSW40RF80EVM 射频评估板上的 DAC38RF80的配置有疑问。 我们将在开发项目中使用此器件组合。 Xilinx 评估板的接口使用单个 GTH 收发器和一个 MTI JESD-204B IP 内核。

我们的测试设置原理图如下所示:

TSW40RF80EVM 电路板的配置通过 TSW40RF80EVM GUI 应用完成。

我们成功地将射频电路板配置为7.3727Gbps 通道速率(JESD 模式12410),并针对“链路配置错误”禁用了同步请求。 该模式不使用 DAC PLL。 然而、这个模式与我们要求一个245.76MSPS 采样率的应用不兼容、因此、我们想要更改为9.8304MHz 通道速率(JESD 模式12410、使用 DAC PLL)、但是不能将这个模式配置为提供适当的输出。 (请注意、我们可以通过私人消息发送频谱图片、并通过 GUI 屏幕转储显示使用的 TSW40RF80EVM 电路板配置和活动警报、 还有一个 Vivado ILA 转储、显示 Xilinx FPGA 中 JESD-204B 内核输出端的 JESD 信令。

另请注意、我们已使用 PRBS7测试模式成功测试了从 Xilinx 电路板到 TSW40RF80的高速链路。 因此、我们期望信号完整性问题得到排除。

我们花费了大量时间来尝试更正配置。 因此、如果您能为获取正确配置提供指导、我们将不胜感激。

此致

Ghafoor