你好!

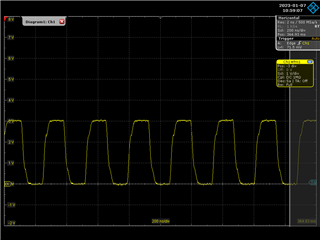

我们在 HART 模式下使用 DAC8742H、并已将 XEN、CLK_CFG0和 CLK_CFG1配置为接受以3.6864MHz 运行的外部 CMOS 时钟源(由函数发生器生成)(数据表16页表1中的第1行)。 根据此配置的说明、我们已在 XTAL1 (X1、引脚28)和 GND 之间连接 CMOS 时钟。 CMOS 时钟的峰峰值振幅为3.0V、偏移为+ 1.5V、因此逻辑低电平为0V、逻辑高电平为+ 3.0V。 SE 屏幕截图#1。

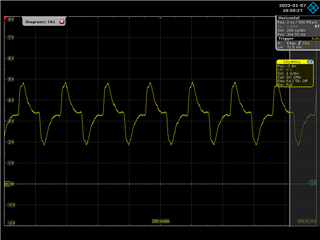

但是、当我们以这种方式将 CMOS 时钟连接到引脚 X1时、在该引脚上测量的时钟信号电平会升至 IOVDD (+ 3.3V)、并且看起来是交流耦合的、请参阅屏幕截图#2。 这是否意味着 CMOS 时钟信号必须与引脚 X1交流耦合? 我看不到数据表提到了这一点。

祝您度过美好的一天,并提前感谢您的回答!

此致、

1月