主题中讨论的其他器件: THS4521、 ADS1278

您好!

我正在 使用 Verilog 对 THS1206 ADC 进行编程和读取。 该 ADC 的最终用途是用于压电传感器。 目前、在电路板上、所有默认值均根据数据表进行考虑。 下面 列出了一些未提及的事项:

1.我能否分别将引脚 CS0和 CS1永久连接至 GND 和 VDD? 如果是、需要使用哪些电位(标称0V 和2.5V I s感觉到)?

2.若要在 TL = 1、CONV_CLK = 6MHz、DATA_AV =低电平有效脉冲、VREF =内部连续对话模式、传感器尚未连接的情况下读取单个差分通道(AINP、AINM)(其他未使用)的数据:

RDbar 和 DATA_AV 有效之间的时间间隔应该是多少(因为数据表显示在 DATA_AV 有效但在 CONV_CLK 的下降沿之前读取)?

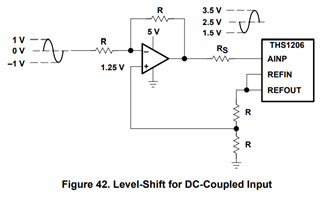

3、上述规格的最小输入范围是多少(两个输入均使用第页上的直流钳位电路进行钳位 36)? 是否可以在我短接/打开输入端子时读取?

4.如果我不钳位、 是否可以通过短接输入实现噪声行为/ENOB/Noise FREE 位?

5.在配置 CRS 时,是否需要任何时间间隔? 能否以连续时钟发送配置字?

谢谢