Other Parts Discussed in Thread: OPA2350, ADS1278, THS4521, OPA350

主题中讨论的其他器件:OPA2350、 THS4521、 OPA350、 REF5020

您好、E2E 专家、

你好。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: OPA2350, ADS1278, THS4521, OPA350

您好、E2E 专家、

你好。

您好!

是的、图89第39页的示例输入放大器电路不仅驱动 ADC 输入、还充当抗混叠滤波器。 假设 CLK 频率为27MHz、它将为 fCLK/4频带内的任何输入信号提供好于55dB 的衰减。

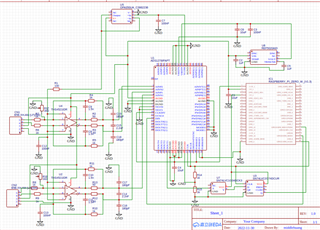

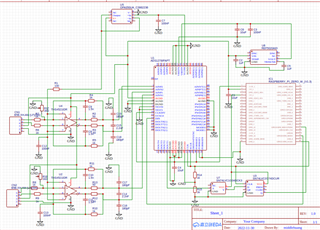

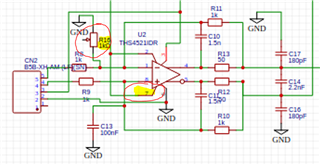

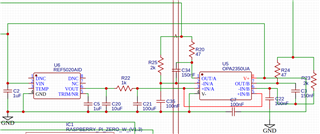

输入放大器有一些原理图误差。

引脚7是断电引脚。 它应该保持悬空或者被连接至+5V 电源、引脚3。

2.不应包含电阻器 R16。 这将导致不平衡的差分信号、并且不会按预期工作。

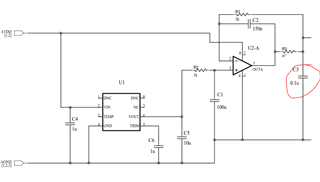

为了 获得最佳性能、基准应该使用一个缓冲电路。 下面的 U2-A 是 OPA2350。

ADC 上有许多缺失的引脚连接。 所有数字输入都需要连接到 IOVDD 或 GND、具体取决于所需的功能。 外部散热焊盘 EP 引脚65需要接地。

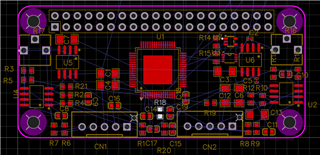

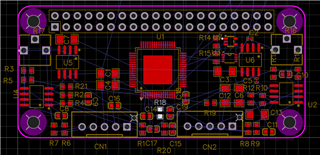

在 布局方面、所有电源旁路电容器、基准电容器和输入电容器应尽可能靠近 ADS1278引脚放置、以提供良好的性能。

6. 对于布局,建议使用单个接地层。 为确保性能可靠、所有 ADS1278接地引脚(AGND 和 DGND)以及散热焊盘应直接连接到 ADS1278封装下方的同一接地层。

客户似乎正在使用帧同步。 如果主机处理器不支持此类接口、则可能很难使其正常工作。 如果设计中所需的最大数据速率为105kSPS 或更低、我建议使用所有处理器都支持的 SPI 模式。 对于 SPI、CLK 频率可设置为27MHz。

客户更新原理图后、请发送更新、我将进行审查。 此外、请与客户确认其设计中需要的最大采样率。

此致、

Keith Nicholas

精密 ADC 应用

您好、Keith、

你好。

您好!

我将在本周工作结束前查看更新的原理图。 所述的更改应能正常工作。 将 THS4521的引脚7悬空时不应出现任何问题;该引脚在内部上拉为高电平、默认为上电状态。

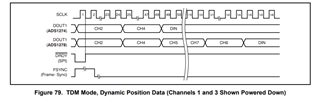

不需要 RTOS、但应使用中断例程来监控 ADS1278的 DRDY 输出信号。 在 DRDY 的下降沿触发中断例程、然后根据需要将数据从 ADC 输出时钟。 您可以使用 format=010、但您的处理器上需要单独的 SDI 输入。 由于您以低数据速率(2000sps 或更低)运行、我建议使用 format=000、它将在单个 SDO 线路上发送所有数据。

关于 R16、适应不同传感器输出范围的最佳方法是添加一些额外的缓冲器。 我将在明天查看更新的原理图时提供建议的输入电路。

谢谢、

Keith

您好!

由于这是一种具有两个通道的 IEPE 数据采集设计、我建议查看适用于 IEPE 传感器的全新 TI 参考设计。

尽管此设计支持4个通道、但也可以轻松修改以支持2个通道。 它包含用户指南、其中包含原理图和建议的电路板布局。

此致、

Keith

您好、Keith、

你好。

您好!

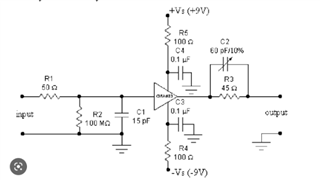

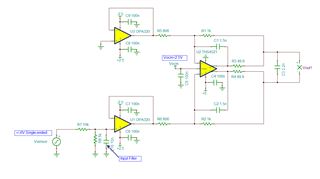

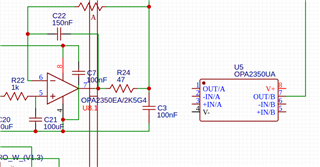

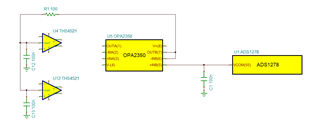

ADS1278的输入放大器可将+/-6V 单端输入转换为 ADS1278的满量程输入范围、即+/-2.5V 差分。 下面是一个可以实现此目的的电路。

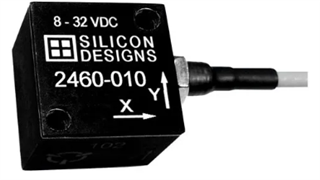

如果您使用的是 Silicon Labs 传感器、则输出已经是差分的、并生成+/-4V 差分的满量程输出、共模为2.5V。 如果使用此传感器、则以下电路将正确缩放输出。

传感器的带宽限制为2kHz。 您可以在第一级放大器输入端添加一个单电容器、以创建一个额外的低通滤波器、该滤波器应可为任何混叠信号提供超过80dB 的衰减。

是的、对于数字通信、您必须监控 DRDY 引脚的状态。 当这个引脚变为低电平时、它表示转换结果完成并且主机处理器应该读取数据。 如果处理器足够快、则可以轮询该引脚、或者更常见的情况下、使用硬件中断。

当使用 格式模式= 000时、所有通道的数据将在 DOUT1引脚上输出。 有关更多详细信息、请参阅图79。

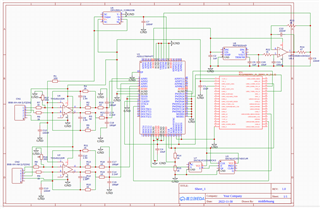

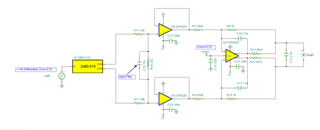

对于您的原理图设计、以下是应进行的几处更正。

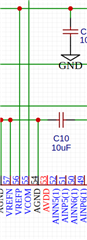

对于 基准引脚、在 ADS1278 VREFP 和 VREFN 引脚旁边直接添加一个额外的10uF 电容。

2. U5可在 U8.1中替换为附加通道。 OPA2350是 OPA350的双通道版本。

3. 在所有 IC 电源引脚上添加一个0.1uF 电源旁路电容器、包括 U8 (引脚8至引脚4)、U5 (引脚7至引脚4)。

4. 在每个 ADS1278 AVDD 电源引脚上添加0.1uF 电源旁路电容器。

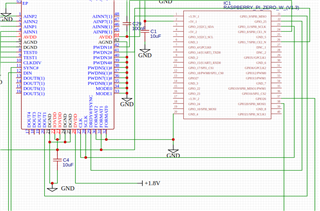

5. SYNC 引脚11应连接到主机处理器上的 IO 引脚。 该引脚可用作器件的复位功能、并应在电源稳定后由处理器切换。

6. 由于您使用的是 SPI 模式,因此可以消除 U7和 U3。 这些附加部件仅在最高速度帧同步模式下运行时才需要。 DOUT1可直接连接到主机处理器的 MISO 输入。

7. DVDD 引脚26是 ADS1278的内部数字电源。 该引脚必须由稳压电压源供电。 请添加一个额外的电源、使用一个线性稳压器来生成一个稳定的+1.8V 电源。

8. CLK 引脚27需要是连续时钟。 该 CLK 的特定频率取决于输出数据速率和所需的运行模式。 如果在高速模式下运行、那么将这个时钟设置为27MHz 将导致一个105ksps 的输出数据速率。

9. DRDY 引脚29需要连接到主机处理器。

AVDD 引脚44和53需要连接到+5V 电源。 还应为每个引脚添加一个0.1uF 电源旁路电容器。

此致、

Keith Nicholas

您好、Keith、

你好。

您好!

输入缓冲器电路看起来正确。 存在一个错误;为了启用放大器、OPA320S 器件的关断引脚5必须连接到 V+(引脚6)。 引脚5 (SHDN)连接悬空

此时、设计中的其他一切看起来都很好。

此致、

Keith

您好、Keith、

你好。

您好!

使用27MHz 时钟(引脚27随附连续27MHz 时钟)、高速模式下的输出数据速率(引脚33和34接地)将导致输出数据速率为105.469ksps。 该输出数据速率决定了数字滤波器的带宽、该带宽等于数据速率的0.49、或者:

F-3dB=105.469*0.49=51.7kHz。 SDI 传感器的最大带宽似乎小于4kHz、因此您的带宽是这些传感器所需带宽的10倍以上。

根据最新版本的原理图、我看到 SCLK 和 CLK 引脚连接在一起。 这些引脚应分开、27MHz 时钟振荡器直接连接到 ADS1278的 CLK 引脚27。

此致、

Keith

您好、Keith、

你好。

您好!

1.看起来是正确的。

2. 是的、可以将+INA/+INB 连接到电路中的同一节点。 这些引脚中的每一个都是高输入阻抗、并且不会加载 RC 滤波器的输出(基准电压的滤波版本)。 但是、您似乎有一个原理图错误。 C35应连接到 R25的另一侧。

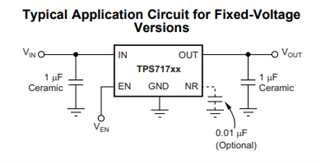

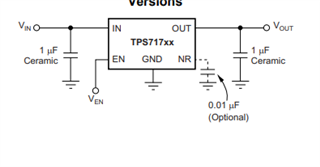

TPS71718是此器件的固定1.8V 输出版本。 您无需将外部电阻器网络连接到 FB 引脚。 实际上、TPS71718的引脚4是降噪(NR)引脚、可保持悬空或连接到10nF 电容器以接地、从而进一步降低噪声。

您将需要估算总电流要求并为您的系统确定适当的功率限制。 我会为5V 电源预算至少100mA 的电流。

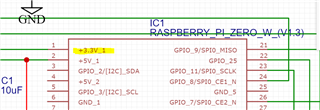

时 钟振荡器需要由与连接到 IOVDD 相同的电源电压供电。 在您的情况下、该时钟振荡器需要由+3.3V 电源供电。

此致、

Keith

您好、Keith、

你好。

您好!

时钟振荡器的输出电压必须与 IOVDD 电源电压的电压电平相同。 如果您使用+1.8V 时钟振荡器、则 IOVDD (以及来自处理器板的数字信号)必须使用1.8V 逻辑电平。 根据您的原理图、您将 IOVDD 连接到+3.3V 电源。 如果是这种情况、则时钟振荡器也必须由+3.3V 电源供电运行。

ADS1278根据时钟频率(f-CLK)、CLKDIV 电平和模式选择设置输出数据速率。 表8显示了可能的最大数据速率。

如果您只需要200sps、那么我建议使用低速模式(MODE0引脚34逻辑高电平和 MODE1引脚33逻辑高电平)、并按如下方式降低 CLK 引脚频率:

对于低速模式、F-DATA=f-CLK/2560、CLKDIV=1。

F-CLK=f-data*2560=200*2560=512kHz。 如果使用标准1MHz 频率时钟、则数据速率为:

F-data=1MHz/2560=390sps。

为了实现数据速率的灵活性、您可能需要为引脚33和34使用上拉和下拉电阻器、以实现不同的速度模式配置。

当数据准备好通过 SPI 从器件中读取时、ADS1278会持续转换数据、将/DRDY 引脚29拉低。 处理器需要监测/DRDY 信号并在/DRDY 变为低电平后传输数据。

此致、

Keith

您好、Keith、

你好。

您好!

是的、可使用任何为+3.3V 运行额定的提供 CMOS 输出的时钟振荡器。 可使用 HX2127002Q 或 HSO321S_27MHz。 ADS1278根据 f-CLK 频率以及 CLKDIV 和 MODE 引脚设置来控制数据速率。

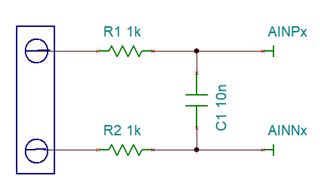

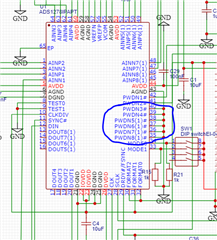

如果要使用未使用的 ADC 通道、需要通过将 PWDNx 连接到+3.3V 来启用它们。 对于任何未使用的通道、我建议在螺钉端子与 AINPx 和 AINNx 输入之间添加一个 RC 滤波器。

下面是我对您的原理图的回顾:

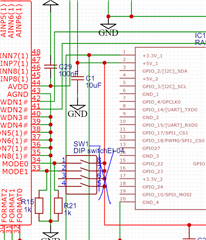

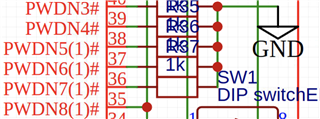

1. 添加 R15和 R21作为下拉电阻器到 MODE 引脚和 DIP 开关是正确的。 但是、DIP 开关需要连接到+3.3V 电源、而不是原理图中所示的+5V 电源。

时钟振荡器 OE 引脚1应连接至 VDD (+3.3V)或保持悬空以启用振荡器的输出。

ADS1278 AVDD 引脚44、REF5020 VIN 引脚2和 OPA2350 V+引脚8需要连接到+5V 电源。 您的原理图中的这些引脚相互连接、但不连接到处理器板的+5V 电源引脚。

此致、

Keith

您好、Keith、

你好。

您好!

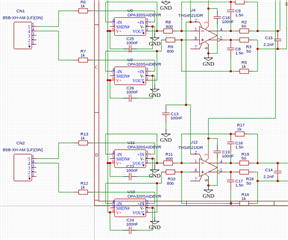

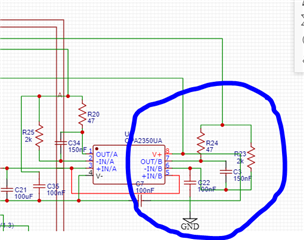

VCOM 缓冲器连接不正确。 ADS1278上的 VCOM 引脚55是输出、应由 U5B 进行缓冲、然后驱动 U4和 U12 (THS4521)的 Vocm 引脚。

以下是正确的原理图连接:

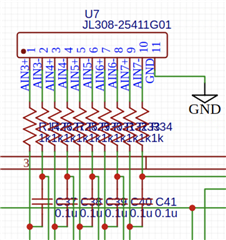

此外,如果您想使用额外的通道,AIN3..... AIN8、那么您需要一个选项来为这些通道加电。 您当前的原理图通过直接接地的 PWDN8引脚连接 PWDN3至 PWDN8、使通道3至8断电。 我建议 为每个数字输入添加下拉电阻器(1k Ω 至接地)、以便您可以选择在稍后为这些通道供电。

此致、

Keith

您好、Keith、

你好。

您好!

ADS1278上的 VCOM 引脚是输出信号。 它是高阻抗输出、因此需要使用放大器进行缓冲。 然后、放大器的输出驱动 THS4521放大器上的 VOCM 输入引脚。

您的原理图更新看起来正确。 如果要启用这些通道、PWDN 引脚需要连接到 IOVDD (3.3V)。 通过添加1k 下拉电阻器、通道将默认为关、但如果移除这些电阻器并向 PWDN 引脚和 IOVDD 添加跳线、则可以启用这些通道。 如果需要、您可以添加另一个开关、就像为 MODE 引脚所做的那样、以轻松启用这些通道。 另一种选择是将这些引脚连接到 RPI 板上未使用的 GPIO 通道、这与您已经对 PWDN1和 PWDN2引脚执行的操作类似。

此致、

Keith