您好!

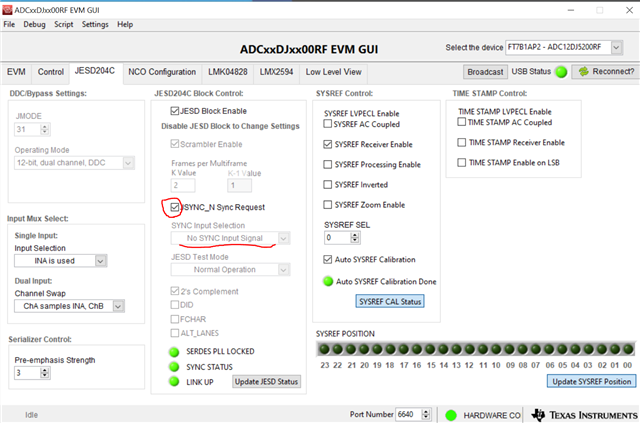

ADCxxDJxx00RF EVM GUI、我可以看到 SERDES PLL 锁定 LED 为绿色。

该 PLL 状态遵循来自外部射频信号发生器的 ADC 采样时钟。

但同步状态和链路启动 LED 为深绿色。

此状态意味着我无法读取串行器/解串器输出数据。

如何调试使 ADC 链路建立的点?

我的设置如下:

JMODE 31.

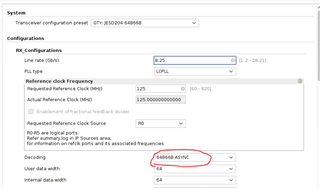

FPGA 参考频率为125MHz

外部 FS 2500MHz

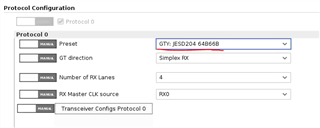

串行器/解串器速率8250MHz

在 FPGA 端:

内核时钟124.751 MHz

Gty Rx 用户时钟124.751 MHz

Sysref 3.906281 MHz

FPGA Gty IBERT 测量值7.997Gbps

谢谢、

Kiman