你(们)好

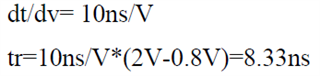

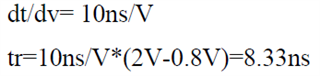

我们需要找出 ADS7049QDCURQ1可能的最大输入上升/下降时间。 因此、我们找到 了 TI 应用手册。 我们了解到、如果我们具有输入转换率以及 VIH (min)和 VIL (max)、那么我们可以使用以下公式得出上升/下降时间:

在这里、VIH (最小值)=2V、VIL (最大值)=0.8V。

这种方法是否正确?

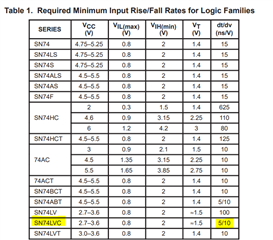

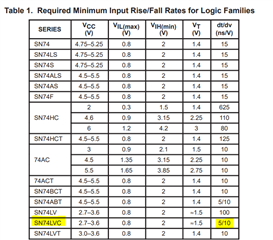

此外 、在 TI 应用手册中、SN74LVC 的转换率(dt/dv)是否意味着0.5ns/V 请确认。

此致

Sreenekshmi。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

我们需要找出 ADS7049QDCURQ1可能的最大输入上升/下降时间。 因此、我们找到 了 TI 应用手册。 我们了解到、如果我们具有输入转换率以及 VIH (min)和 VIL (max)、那么我们可以使用以下公式得出上升/下降时间:

在这里、VIH (最小值)=2V、VIL (最大值)=0.8V。

这种方法是否正确?

此外 、在 TI 应用手册中、SN74LVC 的转换率(dt/dv)是否意味着0.5ns/V 请确认。

此致

Sreenekshmi。

Sreenekshmi、

ADS7049上的 SDO 引脚是器件的唯一数字输出。 未指定 ADS7049 SDO 引脚的最短上升/下降时间。 不过、器件的最大时钟速率已指定、为了使数字通信正常运行、SDO 引脚需要在这段时间的一小部分时间内上升和下降。 最大时钟速率为32MHz (31.5ns)。 为了正常运行、SDO 引脚需要在这段时间的一小部分时间内转换。

请注意、数字信号的实际上升时间将与它们需要驱动的总线电容有关、因此、对于电容更高的较长电阻、上升时间将较慢。

有关5/10ns 的说明。 您可以与逻辑团队确认这一点、但我认为这意味着上升时间为5ns、下降时间为10ns。 我没有看到这方面的确认,但我认为您不应该将5/10设为0.5。

但愿这对您有所帮助。 您能否详细说明您的顾虑?

艺术

Art Kay 感谢您的回答。 实际上、我们正在执行信号完整性分析、因此我们希望接收器规格比较结果并作出判断。 CLK、SDIN 和 CS 是 ADS7049的输入引脚。 因此、我们需要 ADS7049的最大可接受输入上升/下降时间。 因此、我确认了、如果数据表中给出了输入转换率、我们能否使用上述公式计算上升/下降时间。

关于 TI 应用手册中的5/10ns、我将与 Logic 团队确认。

Sreenekshmi、

关于可接受的最大输入上升/下降时间(信号上升的速度):

此致、Art