尊敬的支持团队。

我们无法将 SCLK 写入 ADS1256。

我们的 SCLK 启动 HI、而不是 LO。

这由一个独立于 SPI 接口的 LSI 控制。

例如、使用 SCLK 的复位时序是否可以在没有 SCLK 上升沿的情况下复位?

此致、

Hiroaki Yuyama

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Bryan - San、

感谢你的帮助。

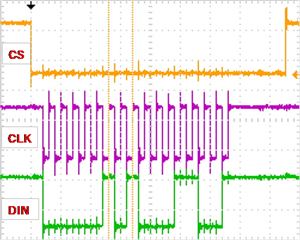

访问(读取/写入) ADS1256时、CS 变为低电平之前、时钟空闲、数据表也是如此

我遵循了发布的时序图。

在我们的 LSI 中、CPOL = 1 (时钟处于高电平空闲状态)、那么我们能否将其连接到与 ADS1256相同的 SPI?

T3 CS 低电平至第一个 SCLK:如果我观察到建立时间和最后一个 SCLK 下降沿之后的 T10 CS 低电平、则时钟空闲时是否可以变为高电平?

我们要求进行确认。

此致、

Hiroaki Yuyama

Hiroaki Yuyama、您好!

[引用 userid="343895" URL"~/support/data-converters-group/data-converters/f/data-converters-forum/1191765/ads1256-sclk-write-timing/4497423 #4497423"]在我们的 LSI 中、CPOL = 1 (时钟处于高电平空闲状态)、因此我们无法将其连接到与 ADS1256相同的 SPI?是的、正确。 ADS1256要求 CPOL = 0

[引用 userid="343895" URL"~/support/data-converters-group/data-converters/f/data-converters-forum/1191765/ads1256-sclk-write-timing/4497423 #4497423"] T3 CS 低电平至第一个 SCLK:如果我在最终 SCLK 下降沿之后观察到建立时间和 T10 CS 低电平、则时钟空闲时可以变为高电平吗?您能否解释一下"时钟空闲时是否可以提高电平"的意思? 您是否在询问时钟空闲时 CS 是否可变为高电平? 您应遵循 ADS1256数据表中的图1所示的 SPI 帧序列和时序。

布莱恩

您好、Bryan - San、

感谢你的答复。

我还有一个问题、当 CS=Hi 时、如果 SCLK 为高电平、是否没有问题?

此外、当 CS=Lo 时、T3 CS 至第一个 SCLK 低电平:观察设置时间和 T10 SCLK 下降沿、时钟空闲时、SCLK 是否可以变为高电平?

'当 CS 为低电平时、请遵循数据表图1中的时序图。'

在 LSI 中、当 CS 为高电平时、SCLK 变为高电平。

此致、

Hiroaki Yuyama

Hiroaki Yuyama、您好!

时钟极性(CPOL)位在"空闲状态"期间定义。 "空闲状态"定义为 CS 处于高电平、在传输开始时转换为低电平、 CS 处于低电平且在传输结束时转换为高电平的周期。

因此、 在 CS 切换为低电平之前、SCLK 必须略为低电平、 而在 CS 变为高电平之后、CS 也必须略为低电平。 我强烈建议您对 ADS1256使用正确的 CPOL 设置、以便 ADC 按预期运行

布莱恩

Hiroaki Yuyama、您好!

正确的是、ADS1256只能使用 SCLK 引脚复位。 但是、这种类型的复位需要在 SCLK 上有一个非常具体的模式、所以我认为这不是问题。

主要问题是、在整个通信帧期间、包括之前和之后的一段时间内、ADC 期望 SCLK 为低电平。 您不能在系统中设置 CPOL = 0有什么原因吗? 您是否在 CPOL = 1的 SPI 总线上有其他器件?

布莱恩