主题中讨论的其他器件:DAC37J82EVM、 DAC37J82、

尊敬的 TI 团队:

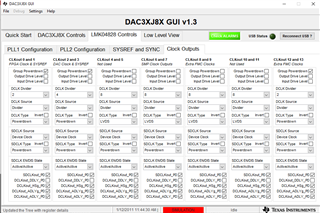

我手上有两个 EVM TSW14J56+DAC37J82。 根据 DAC37J82EVM 用户指南、我可以成功完成快速入门设计。

我们对 DAC37J82使用 LMF=222配置。

在下一步中、我们希望在我们自己的原型中复制此 JESD204B 项目。 我们 现在使用的是 ZYNC7000 FPGA。

您能否告诉我您基于此快速入门设计的 JESD204B 配置? FPGA 和 DAC 端都很感激。

我们的设计中仍然需要 TI JESD204B IP。

此致、

Brooke