您好!

我使用 CS 线路(在不同 CS 上升沿之间更改数据)作为时钟输入数据、而不是 WR 线路。

数据表未描述 WRn 连接至低电平并且 CS_A/BN 被循环以加载数据的情况。

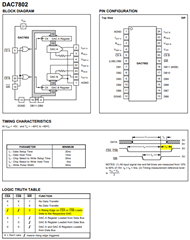

方框图显示 CS 和 WR 在时钟链时序方面在拓扑上是等效的。

对吗?

在使用 CS 加载数据时、是否应该使用不同的设置和保持值(与为 WRn 指定的值不同)?

感谢你的帮助!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我使用 CS 线路(在不同 CS 上升沿之间更改数据)作为时钟输入数据、而不是 WR 线路。

数据表未描述 WRn 连接至低电平并且 CS_A/BN 被循环以加载数据的情况。

方框图显示 CS 和 WR 在时钟链时序方面在拓扑上是等效的。

对吗?

在使用 CS 加载数据时、是否应该使用不同的设置和保持值(与为 WRn 指定的值不同)?

感谢你的帮助!

您好、Michael、

我想您正在讨论逻辑真值表中突出显示的情况、这是写入 DAC 的有效方法。

在这种情况下、您只需遵循计时图中针对 CSA 和 CSB 线路显示的 T3和 T4。 我假设器件中有一些额外的逻辑将 CSA-B 与 WR 区分开来、但至少其中一个信号需要保持恒定、另一个信号需要上升沿才能根据真值表加载数据。

如果您使用 WR 信号、则 T5只是告诉您 WR 需要保持低电平30ns 才能识别上升沿并加载数据。 如果保持 WR 被拉至低电平、则无需更改 CSAA/B 的任何时序。

最棒的

Katlynne Jones