您好!

我的客户遇到一个问题、即他们设计的 DAC37J82没有输出。

他们在以下条件下使用 DAC37J82。

- DAC 数据速率输入: 245.76Mhz

-通道: 4 (LMF=421)

-插值: 2.

- DAC 输出速率: 491.52Mhz (DAC CLK 491.52Mhz )

- FPGA JESD CLK : 245.76Mhz

- JESD 线速率设置值:2.4576Ghz

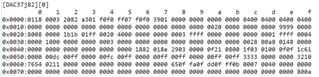

-注册设置

以下是他们检查的内容:

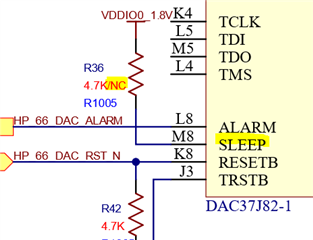

- TX_Enable = 1 & ResetB = 1

- SysRef P/N 输入(JESD_CORE clk / 64、0.96MHz)、警报00

- DAC_SYNC 输出高电平(DAC -> FPGA SYNC 信号为高电平)

- FPGA -> DAC 信号(眼图)

-串行器/解串器 PLL 已锁定

- 4通道对齐警报正常(0x64/0x65/0x66/0x67 : 0000).

1.他们还应该检查哪些其他条件来解决 DAC37J82无输出问题?

2.它们仅使用 IOUTx 的 A 和 D。 未使用的 B 和 C 悬空。 不将未使用的 IOUT 连接到 GND 的问题是否与无输出有关?

谢谢你。

JH