主题中讨论的其他器件:OPA4186

尊敬的先生/女士:

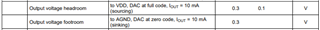

我目前正在使用这一部件设计 SMU 系统。 但是、数据表中 关于输出电压余量的说明不是很清楚。

图32仅 ΔV 了 DAC 电压、而不显示不同负载和不同 DAC 输入下的 Δ I。

由于我将使用该器件来驱动采用同相配置的具有极低偏置电流的运算放大器(OPA4186)、因此我想知道可以接近 VDD 和 GND 的大致程度。

下一个问题: 内部参考默认开启、必须由程序禁用。

如果将一个外部基准(几乎即时开启)连接到 REFIO 引脚并且 处理器需要时间进行初始化、 我可以想象、在禁用内部基准之前、外部基准将会根据内部基准进行驱动。 除了添加串联电阻器、有没有其他解决方案可以解决这个问题? 我认为最好禁用内部基准或者至少降低内部基准缓冲器的输出电流、就像 TI 的一些旧 DAC 一样。

谢谢你。

Eric