我们正在尝试在 Polarfire FPGA Xcvr RX 和 ADC12DJ3200EVM 之间建立连接。

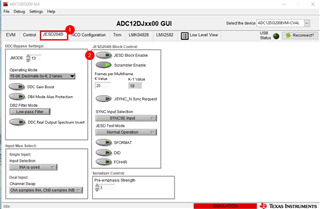

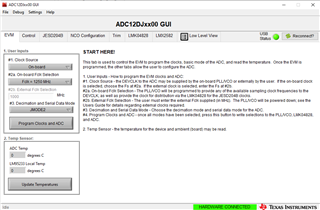

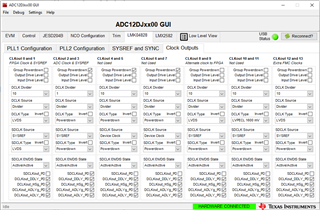

DUT (FPGA)配置: FPGA XCVR 配置为5000Mbps、预期 CDR 参考时钟为125MHz、JESD RX 软 IP 根据 ADC12DJxx00 UG 中提到的 JMODE 设置进行配置。

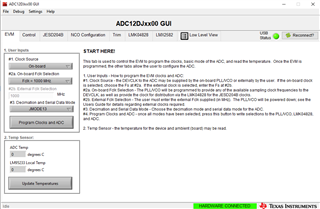

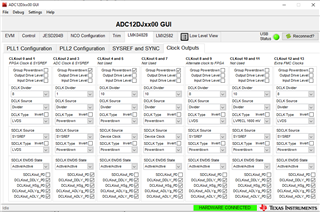

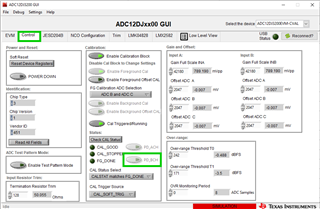

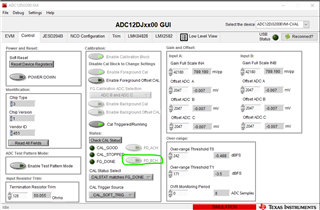

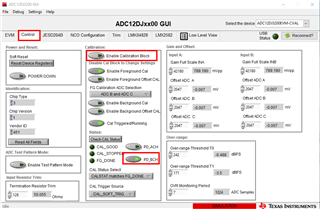

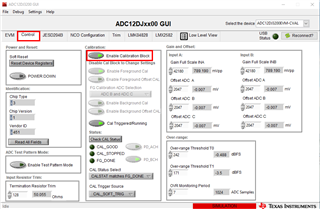

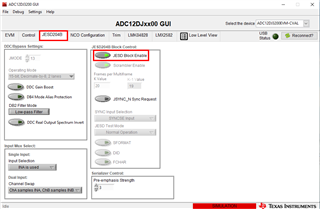

ADC 配置:

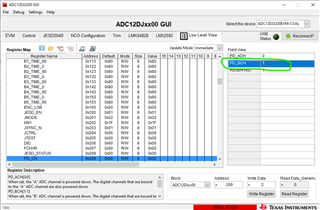

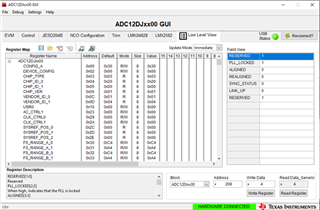

JMODE2: 提供用于 JMODE2的配置(其余选项卡保留原样、以提供默认配置)

-

-

- 板载 Fclk 选择(Fclk)= 1250MHz、DCLK 分频器= 10 -> ADC 的输出时钟= 125MHz

- 对于 JMODE2、我们将观察预期行为(对于 LMFS = 4485)。

- 注意:同样、当我们配置 L = 1时、我们没有看到预期的行为、而不是 L = 4。 是否有方法可以在 JMODE2 (对于 LMFS = 1485)中以单通道模式使用 ADC ?

JMODE13. :

- 对于 JMODE13、我们无法使链接正常工作。

如果我们在此遗漏了任何内容、敬请告知。

谢谢。