主题中讨论的其他器件: ADS1263

我使用 ADS1262进行以下设置

每10次读取 ain0和 ain1上的差分输入

400sps

增益16.

CRC 和状态字节被启用

大约每 12000次读取中有1次(大约每2分钟一次)、我会获得一个读数、其中位全部向左移动1。 这是非常奇怪的、仍然可以通过 CRC 测试、同时会使我的系统混乱、因为错误读取是上一个错误读取结果的两倍。

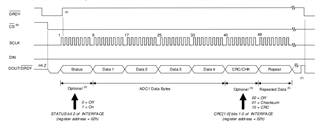

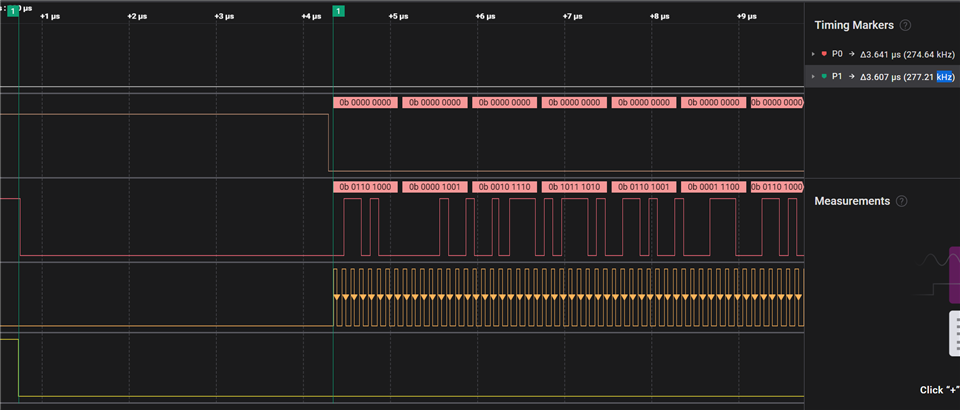

上图是错误读取前的读取。 (顶部到底部 MOSI、MISO、CLK、CS)

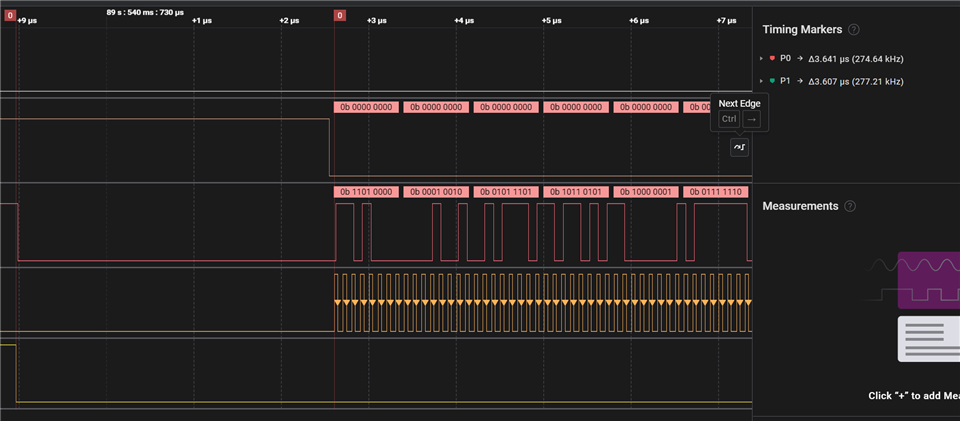

该图像读数在其上面读数后大约10ms。 您可以看到、所有位都向左移动。 我现在可以使用状态位来显示这是不良读取、因为我没有 ads1263。第八位应该始终为0。此外、我使用外部时钟、因此第六位应该为1。 我已经找到了如何希望它不会对我的系统产生影响。 我很好奇这是一个常见问题(发生在我拥有的6块原型板上) 我该怎么做才能解决这个问题? 它在所有时钟频率下都发生、在1MHz 的较低速度下则更加普遍。 目前、我以10 MHz 的频率运行。 我的信号看起来非常干净、所以我在寻找一些建议。