请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC3664EVM 您好,

一位客户需要通过更换 EVM 板来实现以下目标。

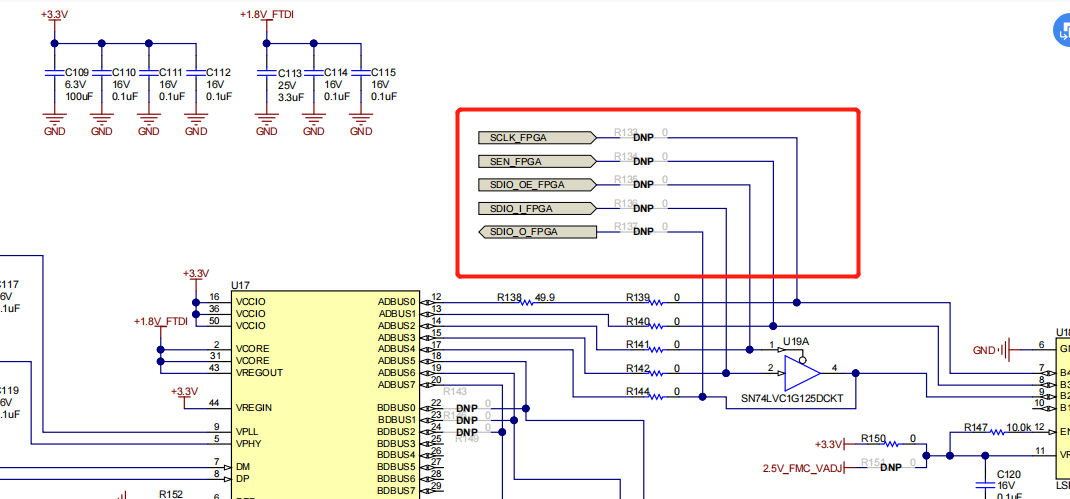

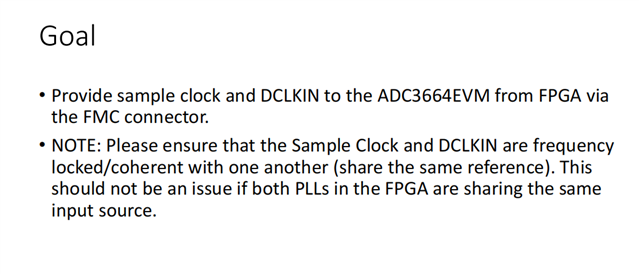

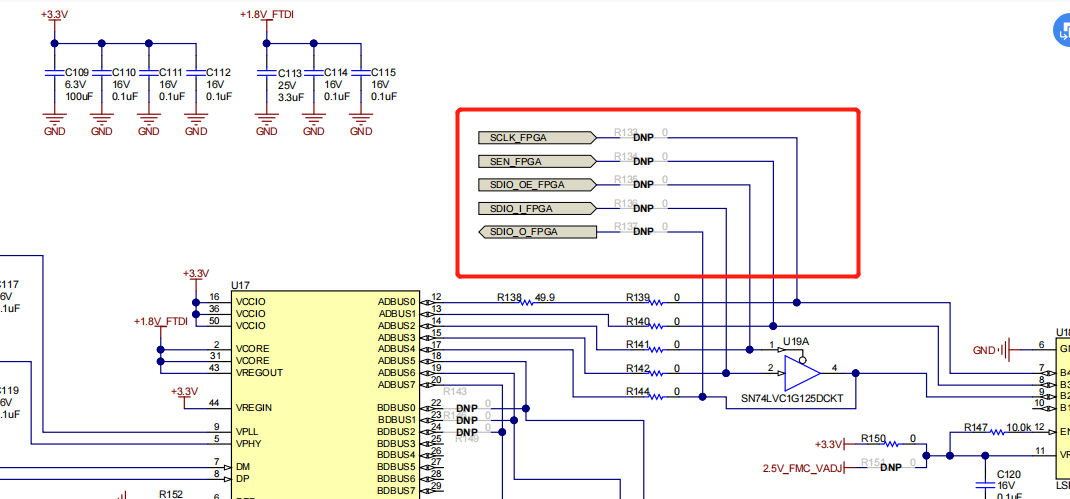

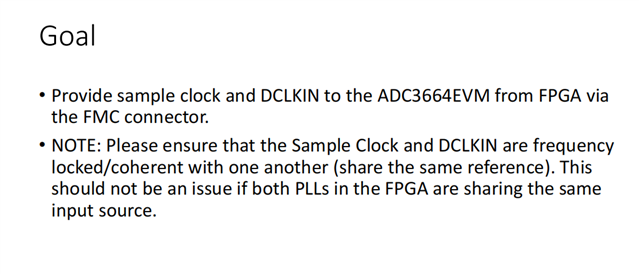

如果他仍然可以使用 GUI 进行配置、他想确认 DCLKIN 和采样信号是否都由 FPGA 提供。 如果需要连接 R133-R137并使用 Verilog 进行 FPGA 配置、则需要1线抽取= 8。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

一位客户需要通过更换 EVM 板来实现以下目标。

如果他仍然可以使用 GUI 进行配置、他想确认 DCLKIN 和采样信号是否都由 FPGA 提供。 如果需要连接 R133-R137并使用 Verilog 进行 FPGA 配置、则需要1线抽取= 8。