Other Parts Discussed in Thread: DDC232

DDC232CKについて質問があります。

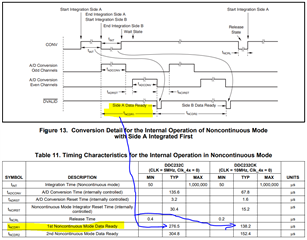

仕様書" 32チャネル、電流入力A / Dコンバータ"のP18のTable11によると、

tncdr1はCLKの周波数で決まるように読み取れます。

仮に20MHzで設定した場合、67.8usになるのでしょうか?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

感谢您用英语书写。

很遗憾、我仍然不清楚您的问题。

可查看数据表第18页、图13和表11。

tncdr1意味着 CONV 的下降沿与/DVALID 的下降沿之间所需的持续时间。 此 tncdr1时间可能具有不同的长度、具体取决于器件(DDC232或 DDC232CK)和 CLK (5MHz 或10MHz)-

不确定67.8us 或20MHz 是什么意思?

谢谢

嗨、简春阳三

感谢您的答复。 抱歉、无法很好地提出问题。

值稍微有误。

至于问题、

数据表第18页、图13和表11是 CLK_4x=0时的规格。

我想了解表11中 CLK_4x=1时的规格。

当我设置 CLK_4x=1时、我读取 DDC232C 的行为如下。

•当 CLK_4x=1时、CLK 的频率增加四倍、因此 CLK 变为20MHz。

•当 CLK 四倍时、tncdr1变为1/4。 因此、276.5/4 = 69.1us。

如果我的解释有任何问题,请告诉我。

您好!

从第3页开始、对于 DDC232C、

如果要设置 CLK_4x=1、系统时钟(CLK)必须介于4至20MHz 之间。

然后、由于 CLK_4x=1、因此时钟分频器= 4、内部时钟频率变为4MHz/4 = 1MHz 至20MHz/4=5MHz、用于生成第14页中讨论的数据有效(/DVALID)信号。 这意味着可能依赖于内部时钟频率的信号现在慢4倍。

第16页显示-

图11至图16。表9 给出了 Clk_4x = 0时的通用时序规格、以 CLK 周期为单位。

如果 Clk_4x = 1、 正如我在 上面的段落中提到的那样、这些值增加4倍、即更长的时间、慢4倍。

因此、以表11的 DDC232C 的 tncdr1为例、如果使用 CLK=5MHz 并设置 CLK_4x= 1、那么 tNCDR1的典型值将变为276.5 * 4 = 1106us 、即速度越来越慢。

谢谢