请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC082S021 产品营销工程师、

我们的客户使用 ADC082S021并看到数字结果比预期值大两倍、但这些数字结果仅在两个通道中的一个通道上显示。

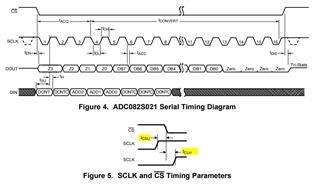

我将查看一些逻辑分析仪捕获结果、以检查 CS 和 CLK 时序。 它们将 MCU 配置为 CLK 在消息之间保持低电平。 当读取结束并且 CS 变为高电平时、时钟刚刚完成其第32个脉冲、这意味着在 CS 变为高电平之前、时钟已经变为高电平然后变为低电平。 这是否可以接受?

我没有看到 CS 变为高电平时要求时钟为高电平的规格、但数据表图5中的图像是这样的。 有要求吗?

谢谢。

达伦