大家好、

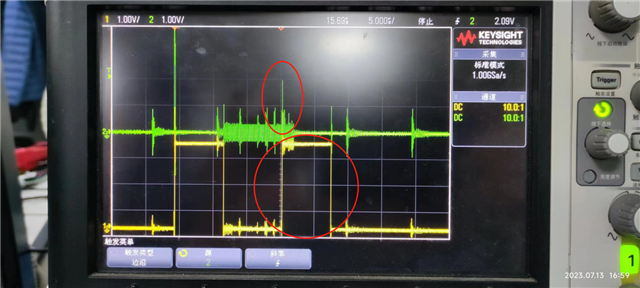

在下图中、绿色曲线为 CONVST、黄色曲线为忙线。 第二个繁忙高电平受异常 CONVST 的影响、客户发现它是由 SCLK 引起、同时此时正在进行转换、因此客户无法使用 ADS8686获得正确的结果。 将 ADS8686更改为 AD7616时、曲线看起来更清晰、并且没有异常 CONVST。

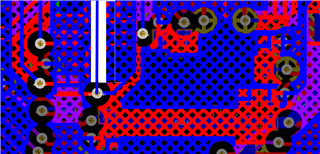

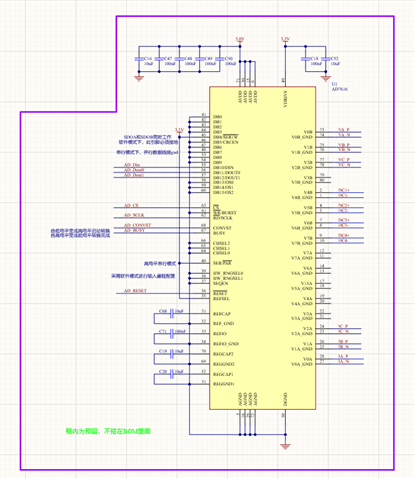

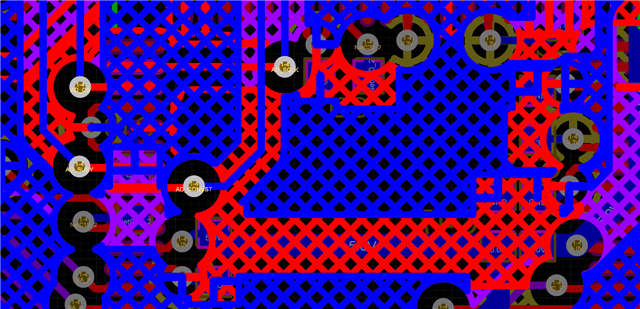

下面是客户的 SCH 和 PCB。 它们直接将 CONVST 和 SCLK 连接到 FPGA、无需任何 RC、因此我建议它们在下一个 PCB 设计中保留 RC。 您是否推荐了 RC 值或其他减少干扰的方法?

B R、

欧文