请求您来帮助我们。

我们在尝试将 Xilinx Zynq UltraScale 电路板连接到 TRF1208-ADC12DJ5200RFEVM。

已进行以下配置

1.要使用外部参考时钟模式、我们按照

第16页上的用户指南说明。

2. GUI 中的 JESD 设置:

JMODE 2、FS 3200MSPS、k =4、SYSREF = 10 MHz、FPGA_Clock = 320MHz、扰频启用、自动参考频率检测启用。

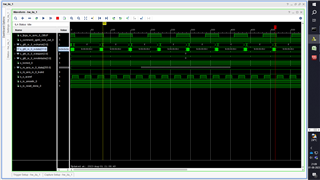

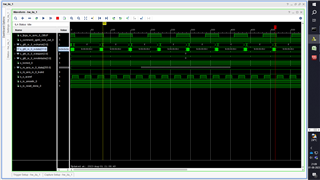

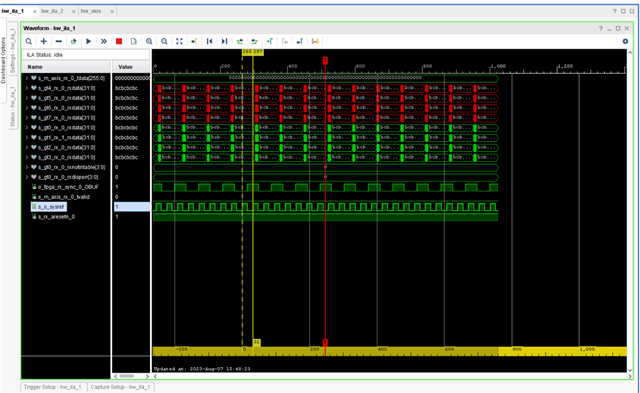

如图所示、我的 SYNC 不断切换。 请帮帮我。

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

请求您来帮助我们。

我们在尝试将 Xilinx Zynq UltraScale 电路板连接到 TRF1208-ADC12DJ5200RFEVM。

已进行以下配置

1.要使用外部参考时钟模式、我们按照

第16页上的用户指南说明。

2. GUI 中的 JESD 设置:

JMODE 2、FS 3200MSPS、k =4、SYSREF = 10 MHz、FPGA_Clock = 320MHz、扰频启用、自动参考频率检测启用。

如图所示、我的 SYNC 不断切换。 请帮帮我。

谢谢

您好、KLN:

以下是需要查看和验证的要点:

此致、

Rob

您好、 Rob Reeder

感谢您的答复。

无效的参考频率是成功退出 CGS 和 ILAS 阶段后持续重新同步的最常见问题。 我们检查了计算结果、10MHz 是有效的参考频率。 请记住、40MHz 是最大值、因此40MHz 的任何整数除法都是合法的。

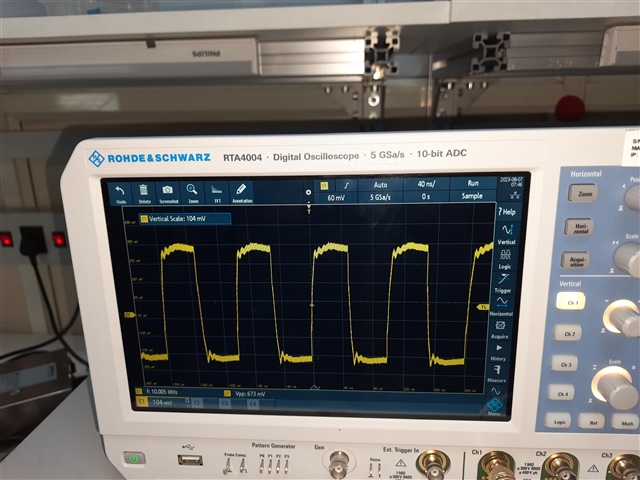

是的、遵循了这一点。 我已经附上了 我们在 ADC SYSREF_IN 上测量的 SYSREF 屏幕截图。

其他想法,可能是信号完整性不佳,这可能会导致链路中断,但鉴于我们的 EVM 上有此数据,除非通过 另一根 FMC 扩展电缆连接,否则我不确定它是不是? 请确认.

ADC EVM 直接安装在 Xilinx ZCU216板 FMC 连接器上。 不涉及扩展电缆。

请尝试增大 K 值以增加弹性缓冲区,但考虑到您将进入数据阶段(超过 ILAS),这应该不是问题。

我们已尝试增加 K 值、结果仍然相同、

您能告诉我们信号发生器是体面的吗? 而不是随机地向 ADC 中添加额外的时钟?

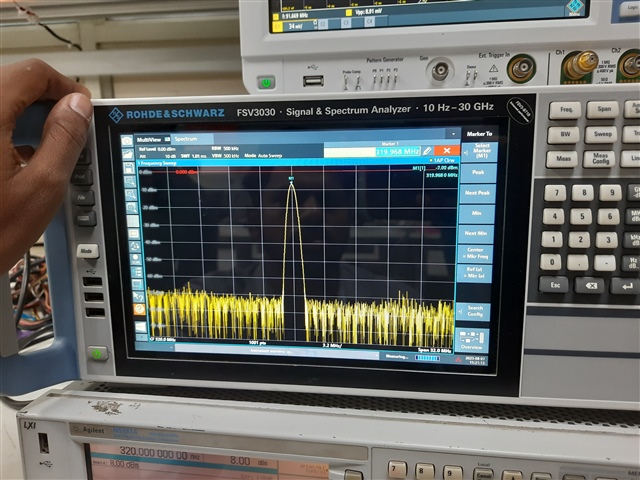

我们已经在频谱分析仪上检查了信号发生器输出、它是干净的时钟.pfa

该值在 LMX 输入时钟处测得(来自外部信号发生器)

另一种可能的情况是 SYSREF 接收器配置不正确。 或者在320MHz 处没有干净的计时关闭、这会导致接收器端出现错误。

我们已将 SYSREF 放在接收器端的芯片示波器中、并对其进行测量(它是320MHz 的32个时钟、相当于10MHz)。 PFA

请发送 配置文件10MHz,以便我们可以验证 LMK sysref 输出是否确实是实际的。 这是否实际使用 LMK 中的示波器测得? 它可能设置错误。

用于配置的 PFA。

e2e.ti.com/.../ADC_5F00_config_5F00_JMODE2_5F00_fs3200.cfg

谢谢。

您好、KLN:

我们使用 Kintex UltraScale+和 Gty 收发器对您的配置进行了测试并修改了时钟、使其适用于我们的参考设计、因为我们没有 Zync US+开发套件。 由于收发器匹配、因此这是我们为复制您的系统所能提供的最佳选择。 我们的基准时钟为160MHz、并且在与您提供的 ADC 配置相同的情况下、我们没有遇到任何同步切换的情况。 我会询问我们团队的其他建议、但我不确定我们还能做些什么。

此致!

埃里克·克莱克纳