Other Parts Discussed in Thread: ADC12DJ3200

主题中讨论的其他器件:ADC12DJ3200

嗨、 团队,

我们客户的问题之一、 您能提供一些故障排除建议吗?

大家好、我们最近已经完成了 ADC12DJ3200调试。 现在我们将开始调试 ADC12DJ5200、其电路完全一致。

首先、我们使用具有以下设置的单通道10G 采样:

ADC12DJ5200使用 JMODE1模式、K=4

JESD_ CORE_ CLK=250MHz

REFCLK=250MHz

ADC_ SYSREF_ CLK=FPGA_ SYSREF_ CLK=31.25MHZ

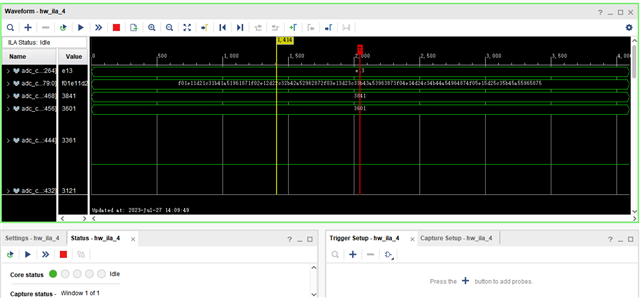

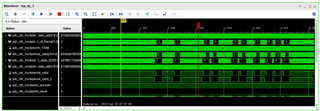

使用传输层测试模式可以发现接收到的数据会出现周期性错误、如 ILA 截获的数据图像所示、并且红色标记点表示错误数据。

接下来、我们尝试9.8G 采样并按如下设置:

ADC12DJ5200使用 JMODE1模式、K=4

JESD_ CORE_ CLK=245MHZ

REFCLK=245MHZ

ADC_SYSREF_ CLK=FPGA_ SYSREF_ CLK=30.625MHZ

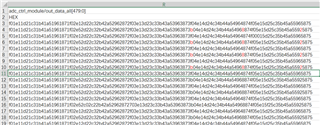

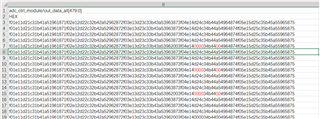

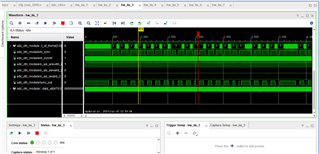

使用传输层测试模式、还可以发现接收到的数据可能具有周期性错误、但错误点与采样10G 时不同。 图中显示了国际法协会截获的数据,红色标记点表示错误数据。

接下来、我们使用8G 采样并按如下设置:

ADC12DJ5200使用 JMODE1模式、K=4

JESD_ CORE_ CLK=200MHz

REFCLK=200MHz

ADC_ SYSREF_ CLK=FPGA_ SYSREF_ CLK=25MHz

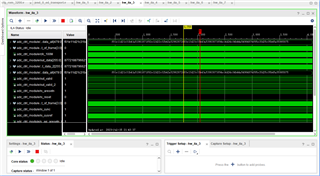

此模式下操作正常、

请问原因可能是甚么?

此致、

罗艾米

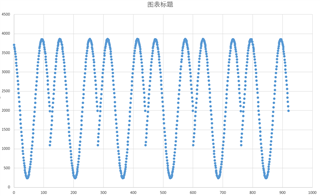

图中显示了部分三角波。

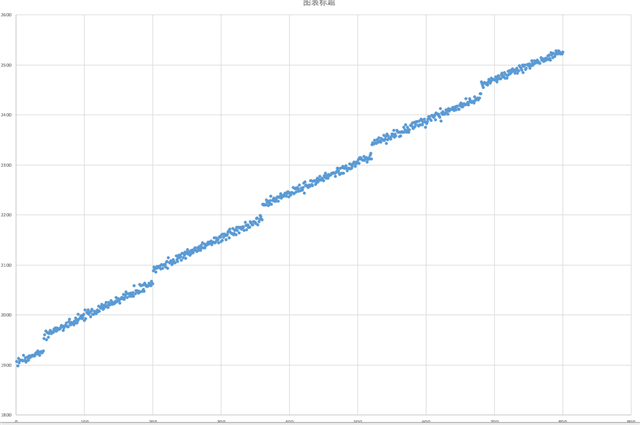

图中显示了部分三角波。