主题中讨论的其他器件:LMK04828、

您好!

我们现在已经构建了电路板、并且正在启动过程中。

原理图以前已经审阅过、但想再次进行检查。

- 在第18页上

- MGTREFCLK0P/N 是 FPGA (接收器)的160 MHz 器件时钟

- FPGACLK1P/N 是 FPGA 的8 MHz SYSREF

- ADCCLKP/N 是 ADC (ADC32J25IRGZT、发送器)的160 MHz 时钟

- SYSREFP/N 是 ADC 的 SYSREF

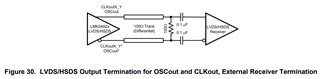

- 它们应该都是 LVDS 吗?

- 如果是、我应该移除 R414和 R415

- 我是否还应该将 R418和 R419更新为0欧姆?

- 是否仍需要 R346和 R347来将 LVDS 连接到 FPGA?

- 之前、幻灯片中提到了

- 通道速率=(FS * 10 * F)/S。当 LMFS = 2221时、为(160M * 10 * F)/1 = 3.2Gbps。 如果您为 K 使用20值、则 SYSREF = FS /(N * K)、其中 N 是任意整数。 如果 N = 1、则 SYSREF = 8MHz。

-

根据 JESD204B 标准、必须满足以下两个公式:

1 < K < 32

17 < F*K< 1024

由于 F 为2、K 至少需要为9。 对 K 使用的值越大、为数据提供的缓冲就越多、但延迟就越大。 某些器件仅允许使用 K 的特定值。

- n 似乎未与任何参数相关联。 则 K 变为任意值。 如何确定 N?

原理图已经过审阅、但您能否再次

- 表2: SYNCP_ADC 和 SYNCM_ADC

- 通过3.3V CMOS 生成

- 表3:FPGACLK1P/N:LMK04828的 SYSREF

- LVDS

- 表5:DAP/M_ADC、DBP/M_ADC 和 GTREFCLK0P/N

- 所有 LVDS

- 表15: ADC32J25IRGZT

- 表18:LMK04828

我认为除同步之外的所有差分信号都是 LVDS。

如果您可以再看一下并确认电路和端接、我将不胜感激。

此致、

安德鲁