Other Parts Discussed in Thread: ADS8668

您好!

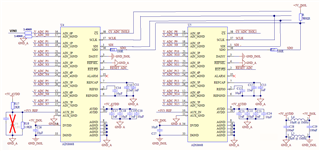

1.我们在星型拓扑中使用2个 ADS8668 DAC。 我们有2个单独控制的 CS、我们通过100R 串联电阻将2个 DAC 的两个 SDO 信号连接在一起、连接图如下。 我们在此配置中遇到 SDO 问题:

*在某种情况下、其中一个 DAC 损坏并持续下拉 SDO (我们已通过移除串联电阻器对其进行了检查)。

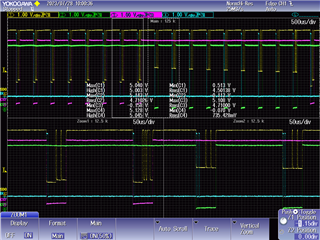

*在另一个案例中,我们已经看到 DAC 不能承载 SDO 0V ,当其中一个 DAC 尝试放置'0'时,我们测量大约1V,当另一个 DAC 尝试放置'0'时,我们测量大约2V。 在所有情况下,它的工作一段时间内都很好,并开始故障后一段时间工作。 我连接了一个针对此问题的示波器截图。

您能否查看连接图、判断是否有问题? 你有什么建议吗?

2.我还有第二个问题,我们需要在所有的 ain_GND 引脚上安装3k48电阻以匹配阻抗。 但我在数据表中看到过、建议直接连接到 GND。 让它采用我们的方式会有问题吗?