Other Parts Discussed in Thread: TSW14J57EVM, ADC12DJ5200SE

主题中讨论的其他器件:TSW14J57EVM、 ADC12DJ5200SE

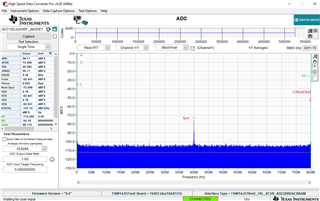

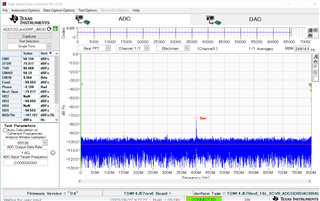

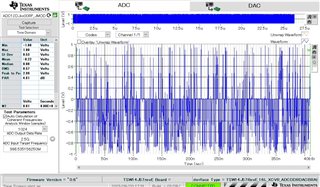

我们无法使用"TSW14J57EVM"和"ADC12DJ500SE EVM"采集高速数据转换器专业版(HSDC)上的数据。 具体而言、我们输入一个10MHz 1Vp-p 正弦波、但可捕获随附图中所示的波形。

您能给我们一些关于如何解决这个问题的提示或建议吗? 我们介绍了以下设置。

HSDC 上的 TSW14J57EVM 设置

FPGA 固件:TSW14J57RevE_16L_Xcvr_ADCBRAMDACDDR.RBF

ADC 文件:ADC12DJxx00RF_JMODE0.ini

ADC 输出数据速率:2.5GHz

ADC 输入目标频率:998.53...MHz

*我们检查"相干频率的自动计算"。

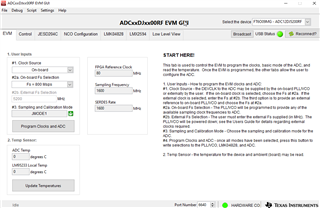

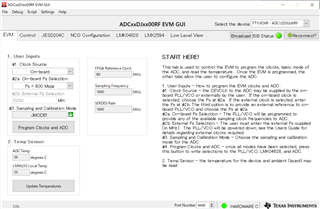

ADCxxDJxx00RF EVM GUI 上的 ADC12DJ500SE EVM 设置

"EVM"选项卡>> 1. 用户输入

#1时钟源:板载*

排名2的板载 FS 选择:FS = 5200Msps

#3采样和校准模式: JMODE0

*我们修复了图7-5中显示的电路部分"slau640b.pdf "。