大家好、

需要向客户说明此 ADC 的数据表。

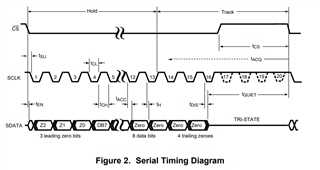

"它表示传输采样需要16个时钟。 三个前导零、八个数据位和四个尾随零。 这是15。 通过查看时序图几乎可以看出、在最终(第16位)的主机计时之前、芯片 tri 会对 MISO 引脚进行状态设置。 对我来说、这意味着三个前导零、八个数据位、四个尾随零和一个未知位。"

这是正确的解释吗? 如果是、什么是未知位? 如果没有,正确的解释是什么?

"同样、数据表说明:"采样位(包括前导 零或尾随零)在 SCLK 的下降 沿随时钟移出、并且打算由接收器在随后的 SCLK 上升沿随时钟移入。" 这清楚地意味着主器件在上升沿捕获数据。 但是 、"如果 CS 在 SCLK 的上升沿之前变为低电平、则 SCLK 的下一个下降沿可能会捕获一个额外的(第四个)零位。" 第4个零位的捕获是什么?

显然有两种情况需要考虑。 当 CS 变为低电平时、SCLK 为低电平、当 CS 变为低电平时、SCLK 为高电平。 我猜、在一个情况下、主器件"捕获"(在上升沿) 3个前导零、8个数据位、4个尾随零和1个垃圾位。 另一个有4个前导零、8个数据位和4个尾随零。"

谢谢!