您好!

当我启用测试图形并启用数字旁路时、我可以在 FPGA 调试环境中看到测试图形。

但禁用旁路。 不再有测试模式、仅保留原始 ADC 数据(相同的情况是关闭测试模式、开启数字旁路)。

是否可以在禁用数字旁路的情况下使用测试模式?

根据数据表图8-48和 ADC35XX EVM GUI 图形、这应该是可能的、但我看到了不同的行为。

非常感谢您提供任何提示。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

当我启用测试图形并启用数字旁路时、我可以在 FPGA 调试环境中看到测试图形。

但禁用旁路。 不再有测试模式、仅保留原始 ADC 数据(相同的情况是关闭测试模式、开启数字旁路)。

是否可以在禁用数字旁路的情况下使用测试模式?

根据数据表图8-48和 ADC35XX EVM GUI 图形、这应该是可能的、但我看到了不同的行为。

非常感谢您提供任何提示。

尊敬的 Drew:

感谢您的观看。

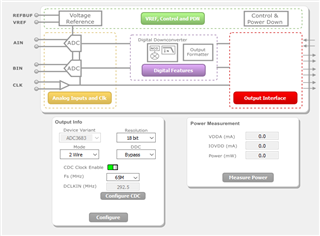

CLKP 为20 MHz

DCLKP 为292、5 MHz

FS 为65 MHz

我要按照以下步骤使用 GUI。

-在"首页"选项卡中

->按"配置 CDC"按钮

-在"Analog Inputs and Clk"选项卡中

-->两个通道的测试模式均更改为"自定义"

-->自定义模式更改为13

-在"数字功能"选项卡中

"数字旁路"默认启用

完成这一步后、我可以在 FPGA 中看到自定义图形13、

现在、更改"Bypass Digital (旁路数字)"开关后、我希望仍然能看到测试模式。 但我会看到原始 ADC 数据。

尊敬的 Robert:

我相信我看到的问题与您的问题相同。 我已经使用斜坡模式进行了尝试、在启用数字旁路时看到了斜坡模式、然后在禁用数字旁路时看到了原始 ADC 输出。 我发现了一点、如果我对实时抽取进行编程(需要禁用数字旁路、即2倍抽取)、并将 DCLK 更改为146.25 MHz、则测试模式会恢复。

我不知道为什么禁用数字旁路后测试图形不会通过。 我将联系设计团队、征求有关这方面的一些意见。 可能需要一两天的时间来获取有关该问题的反馈。

此致、

德鲁

尊敬的 Robert:

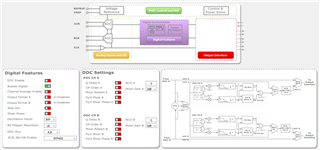

测试模式禁用数字旁路后、应与 DDC 配合使用。 如果未启用 DDC 并配置适当的设置、将不会输出测试模式。

禁用数字旁路时、信号将通过 NCO 和抽取滤波器所在的 DDC 路由。 因此、要穿过该块、必须配置抽取滤波器。

我希望下图清楚地说明了这一点。

再说明一点、即使测试图形发生器在 DDC 块之后、它在禁用数字旁路的情况下不起作用的原因是它需要一个"时钟"才能运行。 在数字旁路模式下、这是 ADC 采样时钟。 禁用数字旁路后不再是这种情况、DDC 会输出一个用于下行处理的时钟(这是抽取因子的函数)。

此致、

德鲁

尊敬的 Drew:

非常感谢您的努力。

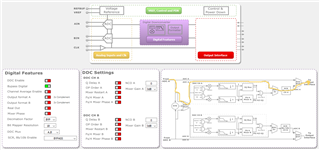

我不明白 TestPatternGenerator 为什么是独立于 DDC 的、因为在图中、这些组件是独立的。 蓝色和红色数据路径路由到连接到 TestPatternGenerator 的多路复用器。

这个多路复用器是否真正像您所描述的一样起作用?

那么、如果禁用数字旁路、禁用 DDC 和启用 TestPattern、哪个路由是正在运行的数据槽? 我可以在下图中看到这条路由。

此致、

罗伯特

GUI 中的图8-48和图数字特性似乎无法搭配使用。

例如

testPattern 发生器:

-在 GUI 中,它被放置在"数字特性"块前面的"模拟输入和时钟"中。

-在图8-48中,它被放置在 NCO 之后, NCO 是"数字功能"块的一部分。

扰频器:

-在 GUI 中,它是"数字旁路复用器"之前"数字功能"块的一部分

-在图8-48中,它是在"数字旁路"之后

这真的很令人困惑、