您好:

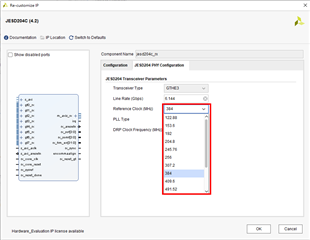

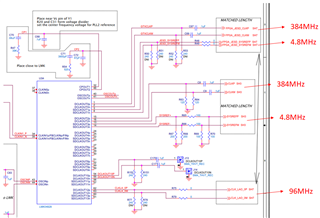

Pic1是用于我的设计的设置。

我使用了板载时钟。

PIC2是来自 LMK04828的输出信号、将时钟输出到 FPGA 和 ADC32RF45。

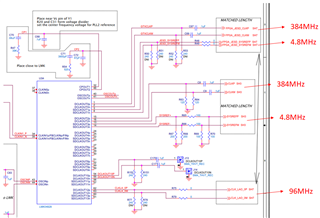

我的问题是 PIC3 LMK04828输出状态、即所有 LED 都应打开?

如果只有 PLL2_LOCKed 的 LED 亮起。 是这样吗?

图1:

图2:

图3:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好:

Pic1是用于我的设计的设置。

我使用了板载时钟。

PIC2是来自 LMK04828的输出信号、将时钟输出到 FPGA 和 ADC32RF45。

我的问题是 PIC3 LMK04828输出状态、即所有 LED 都应打开?

如果只有 PLL2_LOCKed 的 LED 亮起。 是这样吗?

图1:

图2:

图3:

尊敬的 CIOU YUAN:

如果器件在1536MSPS 下并在 LMFS:8-2-8-20下工作,SerDes 速率将为1536M*4 (表14中的 fserdes/fclk 比率)。 JESD 模式选项:旁路模式)。 ADC 本身没有任何锁定标志或状态。 这将必须使用 KCU105的计时向导进行检查。 我想会有一些输出状态选项、例如 PLL 锁定或 PLL 锁定状态、但您需要向 Xilinx 检查这一点、因为我不确定怎么做。

此致、Chase

您好,先生阁下:

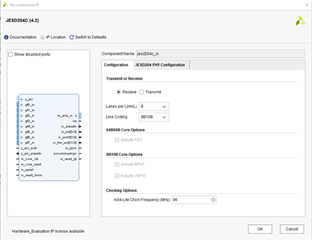

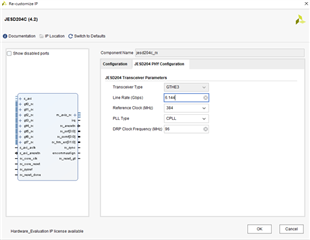

图片1 ~图片3是 Xilinx 的 JESD204 IP 设置值。

我更改了线路速率值、即6.144Gbps。

但在参考时钟(MHz)时、我 在 LMFS:8-2-8-20中使用了紧跟 TI GUI (ADC32RFxx EVM GUI)的384MHz。

FPGA 中的 JESD204_RX 未接收到任何数据、并且 RX 标志 Rx_tvalid 始终为低电平。

有没有人有这种经历?

图片1:

图片2:

图片 3: