数据表中尚不清楚、但您能否确认:

| 数据速率 | 最小 f_clk |

| 4MSPS | 32 MHz |

| 2MSPS | 16 MHz |

| 1MSPS | 8 MHz |

我已经将 ADS1675配置为 CMOS、因此我被限制为1Msps。

我知道 ADS1675的最小/最大规格适用于32MHz、但使用8MHz 时钟与使用32MHz 时钟有没有任何主要缺点?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、McCain:

欢迎加入 TI E2E 社区!

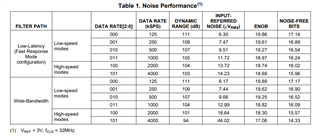

数据表中指定的数据速率基于32MHz 的输入时钟、并将针对每个 DRATE 设置进行线性调整。 根据数据表中的表1、随着数据速率的降低、较低的数据速率使额外输入样本达到平均值、从而实现更低的噪声和更高的动态范围。

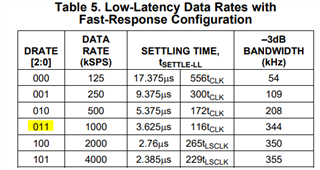

如果将 DRATE 设置为0x011b、则为了获得1MSPS、f-CLK 必须设置为32MHz。 如果 f-CLK= 8MHz、则实际数据速率将降低4倍、即250kSPS。 使用较低的时钟速度、您会得到稍低的功耗、但我们未指定此条件、也没有适用于此条件的数据。

您可以使用 f-CLK=LVDS 并将8MHz 设置为0x000b 以保持1MSPS、但之后数据转换器会自动切换到高速 LVDS 模式、并且您将无法再使用 CMOS 接口。

此致、

N·基思

精密 ADC 应用