您好!

我是 ADC 的初学者、我 想学习如何将 ADC 与 FPGA 连接起来

但在此之前,我想了解它是如何工作的?? 我有 DigSilent 我如何能够使用逻辑分析仪测试 IC 我刚刚绘制了一张线图并将其移动到下面

请告诉我犯的所有错误是什么

此致、

TeX

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Nicholas:

我现在没有原理图、但它连接到了 ADS1278的相同引脚。

我还没有去编程部分进行数据处理、但我只是从控制器生成了 SCLK、并为 IC 提供了所需的输入

查看了 SPI 格式时序图并提供了图中所示的输入、

示波器中的输出是

DOUT 200Hz、DRDY 200Hz 和同步200Hz

根据我的理解、每24位、drdy 应该变低和变高

请告诉我现在犯了什么错误

此致、

TeX

尊敬的 Tex:

FPGA 需要监控 ADS1278的/DRDY 输出。 当/DRDY 从高电平转换为低电平时、已准备好从 ADC 读取数据。

CLK 需要是连续信号;SCLK 将在低电平状态下空闲。 当/DRDY 变为低电平时、FPGA 将生成24个 SCLK、24b 转换结果将位于 DOUT 引脚上。

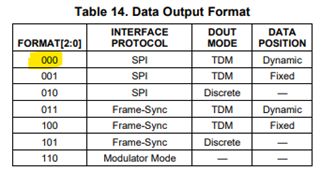

使用 SPI 时、最常见的配置是 TDM 模式、其中所有 ADC 通道都在 DOUT1引脚移出。 在这种情况下、每个 SPI 帧的 SCLK 总数将为8*24=192。 格式引脚需要接地以支持此模式。

以下是操作顺序。

1.监控/DRDY 引脚、等待/DRDY 从高电平变为低电平。

2. 发送192个 SCLK,读取 DOUT1引脚上的数据。

3. 读取数据后,等待下一次/DRDY 从高电平转换为低电平。

假设 CLK=SCLK、27MHz 也可被设定为27MHz。 这将支持高达105468SPS 的数据速率。

正常使用时、SYNC 引脚应保持高电平。 SYNC 引脚用作 ADC 复位、只能用于在上电后和任何模式更改后重新同步 ADC。

为了进一步提供帮助、我需要看到一个展示 ADS1278所有引脚连接的草图。 此外、显示 CLK、SCLK、/DRDY 和 DOUT1信号的波形图也会有所帮助。

此致、

基思

尊敬的 Tex:

随附图像中 DRDY 的频率是多少? 我假设它是200Hz? 此外、所有 IO 信号都应处于 IOVDD 电平或3.3V。 DRDY 是3.3V 吗?

此外、请提供 DRDY 和 SCLK 的示波器捕获、以确保这两个信号之间的时序正确。

我还建议您验证所有电源电压和到 ADS1278的引脚连接。

AVDD 4.75V 至5.25V

DVDD 1.65V 至1.95V

IOVDD 1.65V 至3.6V (我假设这是3.3V)

如果您能提供 ADS1278原理图的屏幕截图、我将进行审阅以确认所有内容都已正确连接。

此致、

基思