你好。 我目前正在测试一个使用 ADC08100转换器的设计。 ADC 数据由 FPGA 进行处理、总共需要24576个连续窗口、并有3072个样本。

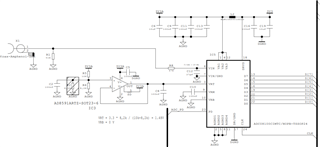

但是、我的数据中出现异常噪音、我想了解原因。 原理图如下所示。

如前所述、我们有一个程序从 ADC 获取3072个样本并将其存储在存储器中。 它进行24576累积数据。

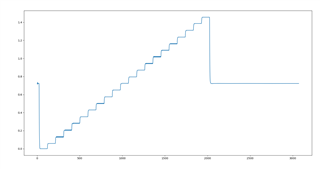

阶梯基准电压的设置范围为1.48V 至0V。

该 ADC 通过一根50 Ω 短同轴电缆连接到波形发生器、并进行正确端接。 以下是一些结果。

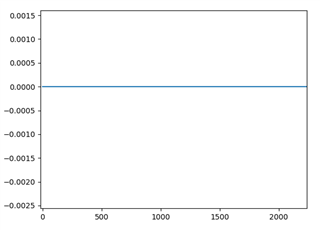

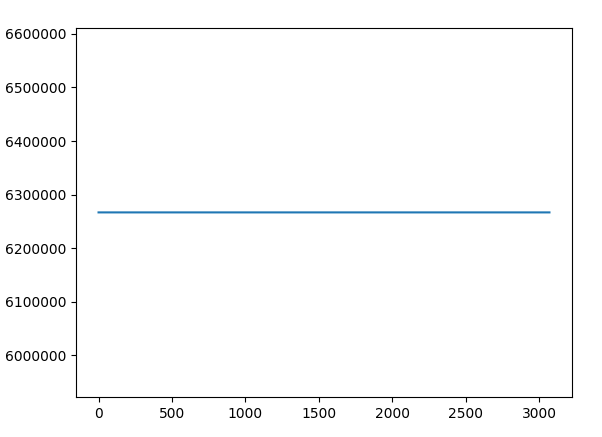

当输入为0V 时稳定。

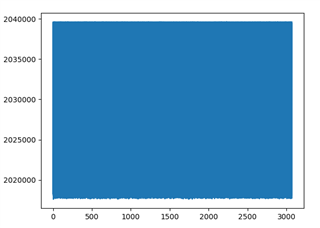

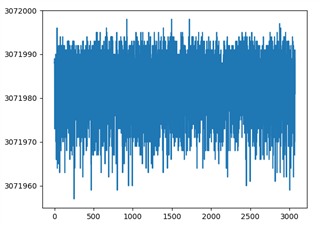

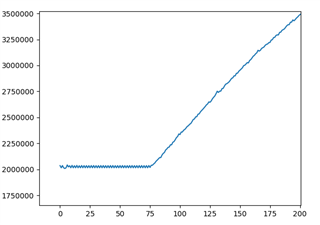

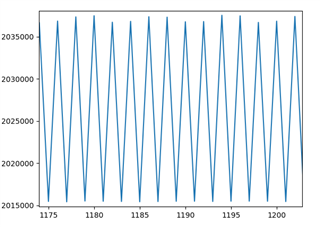

输入为0.5V 时具有高同步噪声

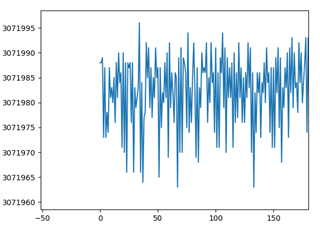

当输入为0.75V 时、看起来更随机的噪声。这就是我对所有测试的预期。 噪声的振幅也要低得多。

当输入为1.5V 时稳定。

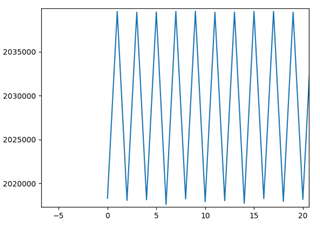

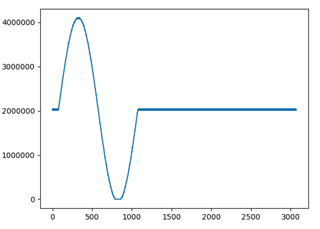

一个周期(0-1V) 100kHz 正弦波、由 FPGA 上的一个引脚触发、与采样窗口开始同步(但具有延迟)。 信号为直流时具有高同步噪声。

这可能是我实施 ADC08100时遇到的问题、也可能是处理系统中的问题? 我认为 FPGA 执行正确、因为结果是可重复的并且看起来是正确的。

注意:当时钟频率降至50 MHz 时、该问题仍然会发生