请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE58JD48 主题中讨论的其他器件:LMK00301、 LMK04832

您好:

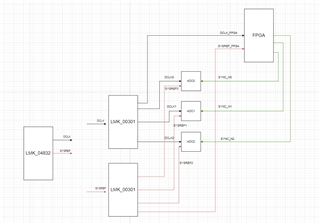

我计划将多个 AFE 与 JESD204B 同步。 目前、我在 PCB 设计中遇到了一些问题、如图所示。 我将使用 LMK04832输出器件的 CLK 和 SYSREF 信号、然后通过 LMK00301将其扇出到 AFE 和 FPGA。 我知道每组器件 CLK 和 SYSREF 信号都应该 进行长度匹配、例如 dclk0和 sysref0。 问题是、DCLK0、DCLK1、DCLK2是否也应该长度匹配、或者是否没有必要? 而对于 FPGA 输出的 SYNC_n 信号、例如 SYNC_n0和 SYNC_n1、它们是否需要 长度匹配?

谢谢