你好。

我们使用 ZCU102和 DAC39J82EVM 作为项目的开发平台、但我们不确定某些参数意味着什么。

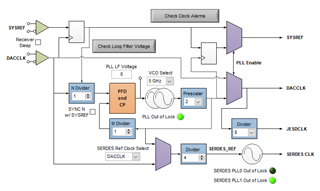

首先、在 DAC3xJ8x 控制的"Clocking"选项卡中: DACCLK、JESDCLK 和 SERDER CLK 之间的区别是什么? 我们的 DACCLK 为2.4576GHz、我们将在2个通道上以6.144Gbps 的通道速度发送307.2MSPS。

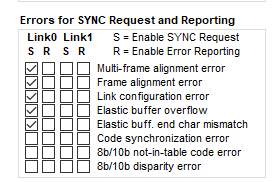

当我们从同步请求设置中选择"代码同步错误"、"8b/10b 不在表中的代码错误"或"8b/10b 视差误差"时、我们还会观察到同步信号变为低电平。

这更可能是由于 FPGA 侧或 DAC 侧的配置错误造成的?

事先感谢、

胡安